Brought to You by

Like the book? Buy it!

# Digitally Assisted Pipeline ADCs Theory and Implementation

*by* Boris Murmann and Bernhard E. Boser

# Kluwer Academic Publishers

DIGITALLY ASSISTED PIPELINE ADCs

This page intentionally left blank

# **Digitally Assisted Pipeline ADCs**

# **Theory and Implementation**

by

# **Boris Murmann**

Standford University

and

# **Bernhard E. Boser**

University of California, Berkeley

KLUWER ACADEMIC PUBLISHERS NEW YORK, BOSTON, DORDRECHT, LONDON, MOSCOW eBook ISBN: 1-4020-7840-4 Print ISBN: 1-4020-7839-0

©2004 Kluwer Academic Publishers New York, Boston, Dordrecht, London, Moscow

Print ©2004 Kluwer Academic Publishers Dordrecht

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at: and Kluwer's eBookstore at: http://kluweronline.com http://ebooks.kluweronline.com Dedication

To our families.

This page intentionally left blank

# Contents

| List of Fi | gures                                           | xi   |

|------------|-------------------------------------------------|------|

| List of Ta | ibles                                           | XV   |

| Acknowl    | edgments                                        | xvii |

| Preface    |                                                 | xix  |

| 1. INTRO   | DDUCTION                                        | 1    |

| 1.         | Motivation                                      | 1    |

| 2.         | Overview                                        | 2    |

| 3.         | Chapter Organization                            | 4    |

| 2. PERFO   | DRMANCE TRENDS                                  | 5    |

| 1.         | Introduction                                    | 5    |

| 2.         | Digital Performance Trends                      | 6    |

| 3.         | ADC Performance Trends                          | 7    |

| 3. SCAL    | ING ANALYSIS                                    | 15   |

| 1.         | Introduction                                    | 15   |

| 2.         | Basic Device Scaling from a Digital Perspective | 16   |

| 3.         | Technology Metrics for Analog Circuits          | 17   |

| 4.         | Scaling Impact on Matching-Limited Circuits     | 25   |

| 5.         | Scaling Impact on Noise-Limited Circuits        | 33   |

| 4. IMPRO   | OVING ANALOG CIRCUIT EFFICIENCY                 | 43   |

| 1.         | Introduction                                    | 43   |

| 2.         | Analog Circuit Challenges                       | 43   |

| 3.         | The Cost of Feedback                            | 45   |

| 4.               | Two-Stage Feedback Amplifier vs. Open-Loop Gain Stage | 46  |

|------------------|-------------------------------------------------------|-----|

| 5.               | Discussion                                            | 52  |

| 5. OPEN-         | -LOOP PIPELINED ADCS                                  | 53  |

| 1.               | A Brief Review of Pipelined ADCs                      | 53  |

| 2.               | Conventional Stage Implementation                     | 54  |

| 3.               | Open-Loop Pipeline Stages                             | 55  |

| 4.               | Alternative Transconductor Implementations            | 60  |

| 6. DIGIT         | AL NONLINEARITY CORRECTION                            | 63  |

| 1.               | Overview                                              | 63  |

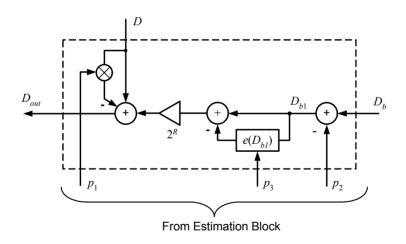

| 2.               | Error Model and Digital Correction                    | 65  |

| 3.               | Alternative Error Models                              | 74  |

| 7. STATI         | STICS-BASED PARAMETER ESTIMATION                      | 75  |

| 1.               | Introduction                                          | 75  |

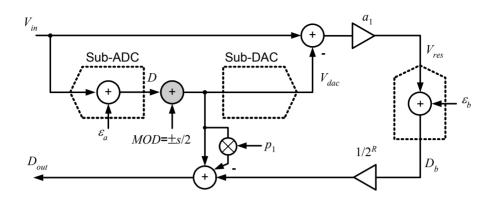

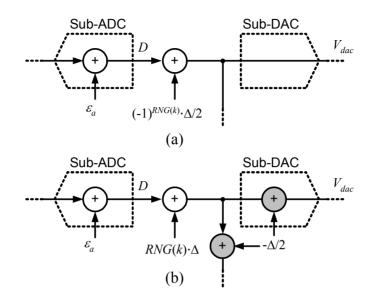

| 2.               | Modulation Approach                                   | 76  |

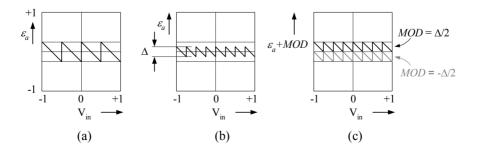

| 3.               | Required Sub-ADC and Sub-DAC Redundancy               | 77  |

| 4.               | Parameter Estimation Based on Residue Differences     | 79  |

| 5.               | Statistics Based Difference Estimation                | 84  |

| 6.               | Complete Estimation Block                             | 87  |

| 7.               | Simulation Example                                    | 90  |

| 8.               | Discussion                                            | 97  |

| 8. PROTO         | OTYPE IMPLEMENTATION                                  | 101 |

| 1.               | ADC Architecture                                      | 101 |

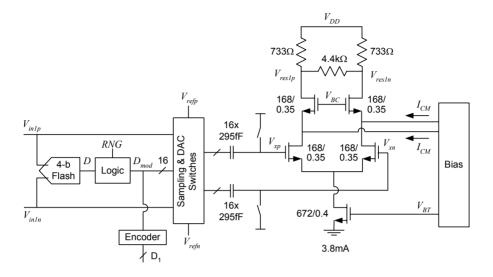

| 2.               | Stage 1                                               | 102 |

| 3.               | Stage 2                                               | 106 |

| 4.               | Post-Processor                                        | 107 |

| 9. EXPER         | RIMENTAL RESULTS                                      | 109 |

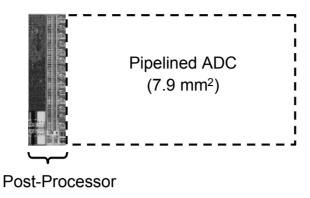

| 1.               | Layout and Packaging                                  | 109 |

| 2.               | Test Setup                                            | 111 |

| 3.               | Measured Results                                      | 112 |

| 4.               | Post-Processor Complexity                             | 121 |

| 10. CON          | CLUSION                                               | 123 |

| 1.               | Summary                                               | 123 |

| 2.               | Suggestions for Future Work                           | 124 |

| Appendic         | es                                                    |     |

| A- Open-         | Loop Charge Redistribution                            | 127 |

| <b>B-</b> Estima | ator Variance                                         | 131 |

| C- LMS Loop Analysis |                         | 137 |

|----------------------|-------------------------|-----|

| 1. Time Constant     |                         | 137 |

| 2.                   | Output Variance         | 138 |

| 3.                   | Maximum Gain Parameters | 139 |

| Referen              | ices                    | 143 |

| Index                |                         | 153 |

This page intentionally left blank

# List of Figures

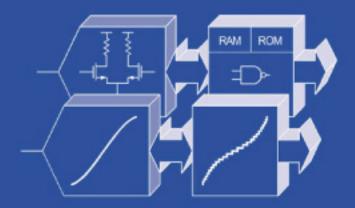

| <i>1-1</i> .  | System overview.                                                        | 3  |

|---------------|-------------------------------------------------------------------------|----|

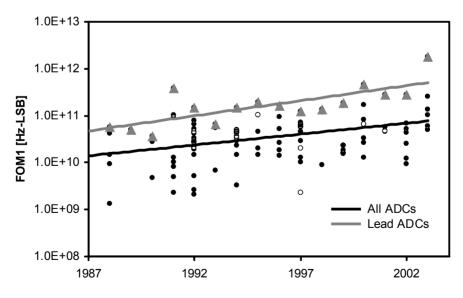

| 2-1.          | ADC performance trend.                                                  | 10 |

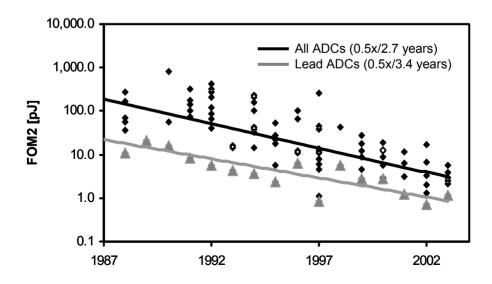

| <i>2-2</i> .  | ADC energy efficiency trend.                                            | 11 |

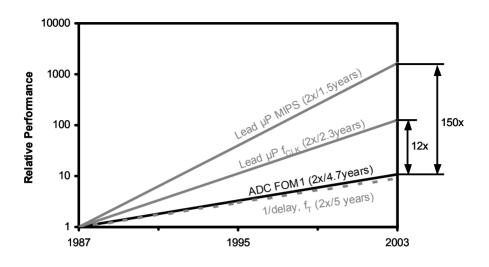

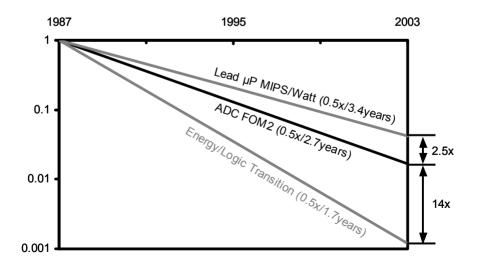

| <i>2-3</i> .  | Comparison of speed trends: ADCs versus digital.                        | 12 |

| 2-4.          | Comparison of energy efficiency trends: ADCs versus digital.            | 12 |

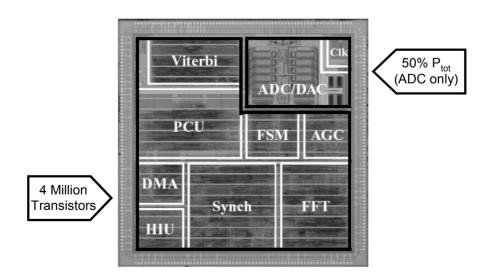

| 2-5.          | Modern ADC application: 802.11 base band processor for                  |    |

|               | wireless networks [21].                                                 | 13 |

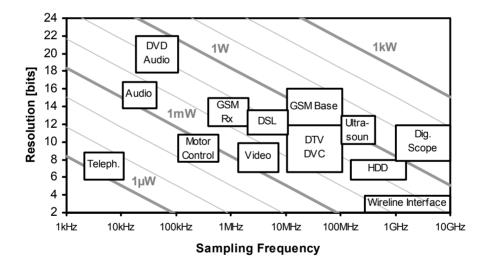

| 2-6.          | ADC applications in the speed/resolution space. The equi-               |    |

|               | power contours assume FOM2=3pJ/conversion.                              | 14 |

| 3-1.          | Supply voltage scaling.                                                 | 18 |

| <i>3-2</i> .  | NMOS transit frequency.                                                 | 19 |

| 3-3.          | Transconductor efficiency versus gate overdrive. The dotted             |    |

|               | line shows the case for perfect square law devices.                     | 20 |

| <b>3-4</b> .  | Product $g_m/I_D f_T$ .                                                 | 21 |

| 3-5.          | NMOS intrinsic device gain at $V_{OV}$ =200mV.                          | 22 |

| 3-6.          | NMOS intrinsic device gain at $V_{OV}$ =200mV (Zoom into typical        |    |

|               | operating region).                                                      | 22 |

| 3-7.          | Technology scaling trends of $A_{VTH}$ and $A_{\beta}$ .                | 24 |

| <i>3-8</i> .  | Flash ADC block diagram.                                                | 26 |

| 3-9.          | Preamp/latch model.                                                     | 27 |

| <i>3-10</i> . | Flash ADC energy as a function of sampling rate (assuming               |    |

|               | constant mismatch factors $A_{VTH}$ , and $A_{\beta}$ ).                | 29 |

| <i>3-11</i> . | Flash ADC energy as a function of sampling rate (assuming               |    |

|               | improving mismatch factors $A_{VT}$ , and $A_{\beta}$ with technology). | 30 |

| <i>3-12</i> . | Estimated flash ADC energy versus feature size (from speed              |    |

|               | trajectory in Figure 3-11).                                             | 31 |

|               |                                                                         |    |

| <i>3-13</i> . | Published flash ADC performance vs. technology.                                | 32 |

|---------------|--------------------------------------------------------------------------------|----|

| 3-14.         | Basic amplifier model.                                                         | 34 |

| 3-15.         | Noise limited circuit energy versus speed and technology.                      | 36 |

| 3-16.         | Ratio slewing/linear settling time vs. sampling speed.                         | 38 |

| <i>3-17</i> . | Noise limited circuit energy with slewing included.                            | 39 |

| <i>3-18</i> . | Published 10-bit pipelined ADC performance vs. technology.                     | 40 |

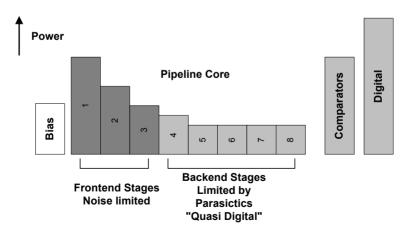

| <i>3-19</i> . | Typical 10-bit pipelined ADC power distribution.                               | 41 |

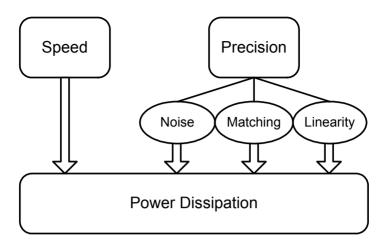

| <i>4-1</i> .  | Analog circuit challenges and power dissipation.                               | 44 |

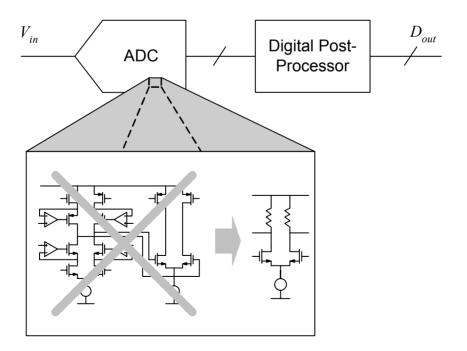

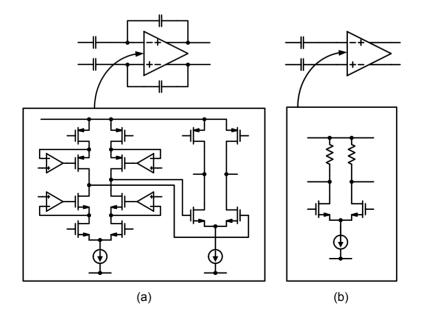

| <i>4-2</i> .  | Comparison: (a) Precision feedback amplifier. (b) Open-loop                    |    |

|               | amplifier.                                                                     | 45 |

| <i>4-3</i> .  | (a) Two-stage feedback amplifier. (b) Open-loop gain stage.                    | 46 |

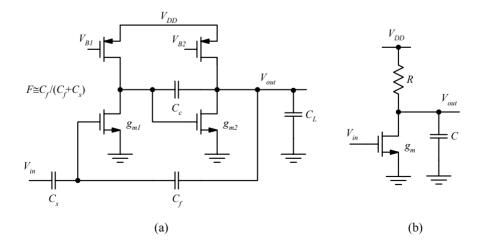

| <i>4-4</i> .  | Two-stage amplifier penalty factor.                                            | 49 |

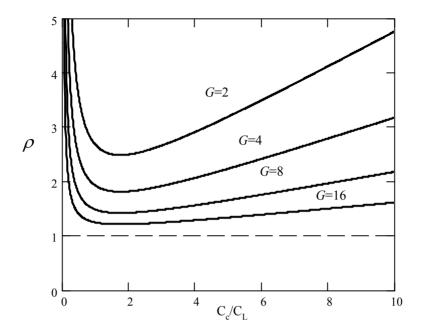

| <i>4-5</i> .  | Percent power savings with open-loop amplification as a                        |    |

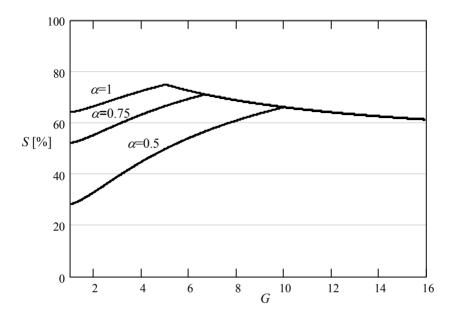

|               | function of gain (assuming $\eta_a = \eta_b$ ).                                | 50 |

| <i>4-6</i> .  | Percent power savings with open-loop amplification as a                        |    |

|               | function of gain (assuming $V_{ref}=1V$ , $\eta_a=10V^{-1}$ and $\eta_b$ given |    |

|               | by (4-13)).                                                                    | 52 |

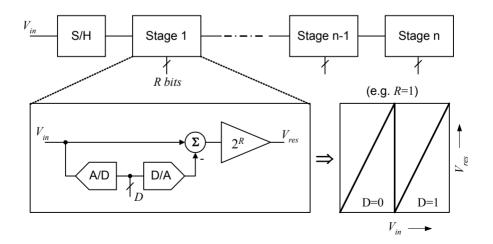

| 5-1.          | Pipelined ADC block diagram.                                                   | 53 |

| 5-2.          | Conventional pipeline stage.                                                   | 55 |

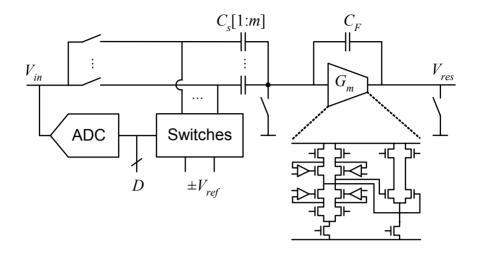

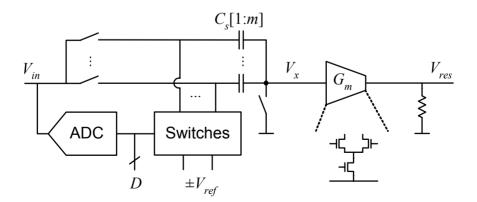

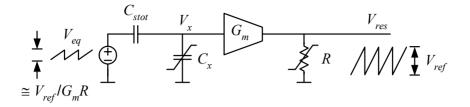

| 5-3.          | Open-loop pipeline stage.                                                      | 56 |

| 5-4.          | Open-loop stage model.                                                         | 57 |

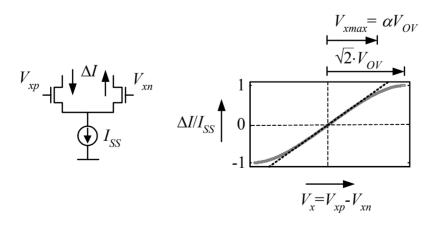

| 5-5.          | Differential pair V-I characteristic.                                          | 58 |

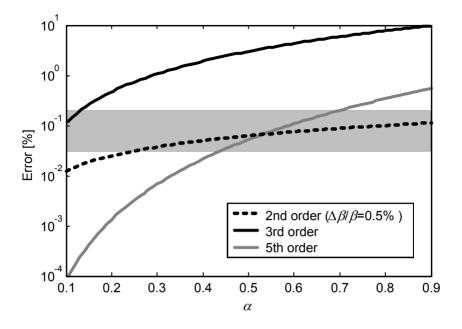

| 5-6.          | Differential pair nonlinearity as a function of $\alpha = V_{xmax}/V_{OV}$ .   | 59 |

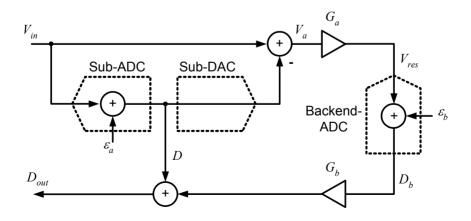

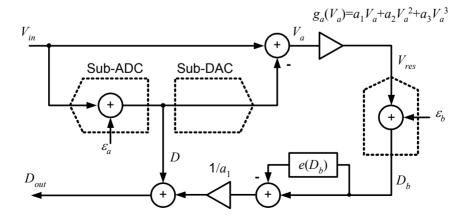

| 6-1.          | (a) ADC block diagram. (b) Reduced model for analysis.                         | 64 |

| 6-2.          | Reduced model with stage sub-circuits.                                         | 65 |

| 6-3.          | Model for error compensation.                                                  | 68 |

| 6-4.          | Additive nonlinearity compensation.                                            | 69 |

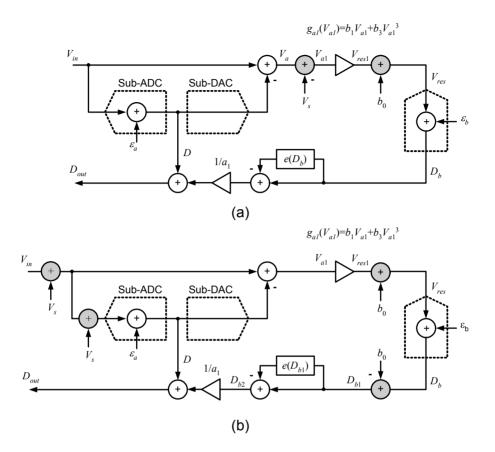

| 6-5.          | (a) Model with shifted variables. (b) Equivalent/compensated                   |    |

|               | model.                                                                         | 71 |

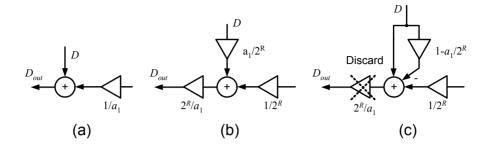

| 6-6.          | Modification for hardware efficient linear digital weighting.                  | 73 |

| 6-7.          | Complete digital correction hardware.                                          | 73 |

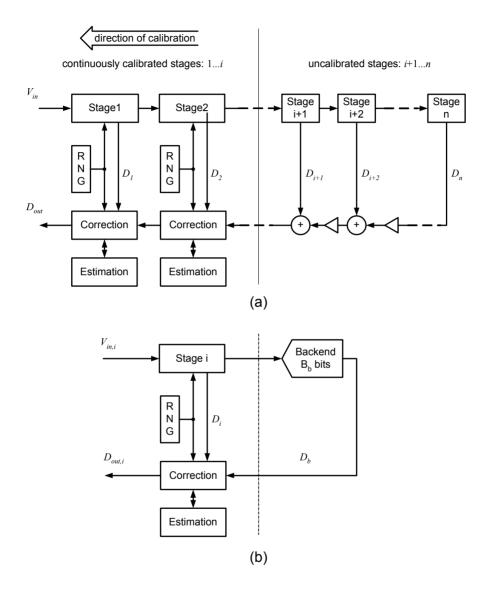

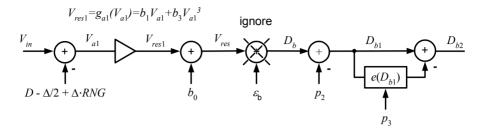

| 7-1.          | System model with digital code modulation.                                     | 77 |

| 7-2. I        | ntroducing Sub-ADC redundancy: (a) Quantization error of a                     |    |

|               | 2-bit sub-ADC. (b) Error of a $(2+1)$ -bit sub-ADC. (c)                        |    |

|               | Superimposed modulation.                                                       | 78 |

| 7 <b>-</b> 3. | Sub-ADC/DAC interface: (a) Bipolar modulation.                                 |    |

|               | (b) Equivalent unipolar modulation with DAC offset.                            | 79 |

| 7-4.          | System model for transfer function analysis.                                   | 80 |

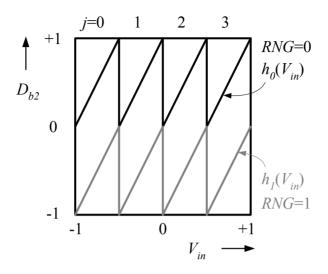

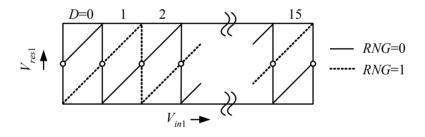

| 7-5.          | Residue plot for both <i>RNG</i> states.                                       | 81 |

| 7 <b>-</b> 6. | Single transfer function segment without correction and                        | 01 |

|               | $b_3 < 0, b_0 = 0.$                                                            | 81 |

|               | - J                                                                            | 01 |

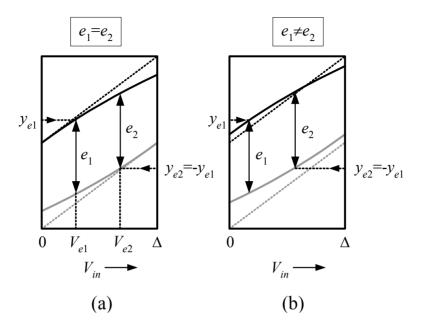

| 7-7.           | Difference measurement with symmetrical ordinates ( $b_3 < 0$ , $b_0=0$ ). (a) Symmetry with ( $b_0=0$ ). (b) Asymmetry caused |              |

|----------------|--------------------------------------------------------------------------------------------------------------------------------|--------------|

|                | by $b_0 \neq 0$ .                                                                                                              | 83           |

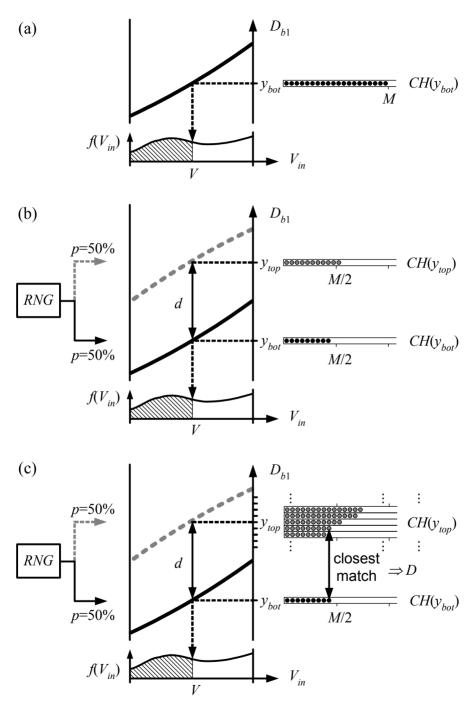

| 7-8.           | Statistics based distance estimation. (a) Cumulative count with <i>RNG</i> fixed. (b) Random split with active <i>RNG</i> .    |              |

|                | (c) Distance estimate from closest cumulative count.                                                                           | 85           |

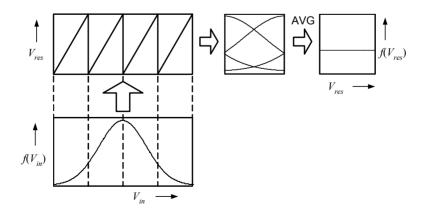

| 7 <b>-</b> 9.  | Averaging effect.                                                                                                              | 87           |

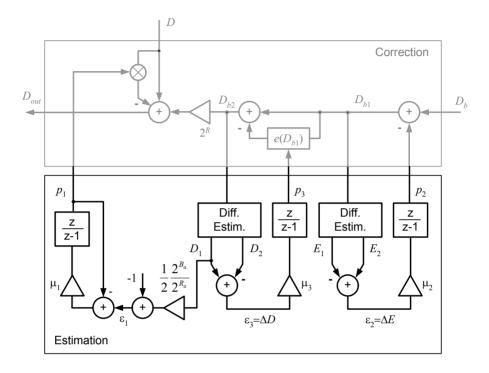

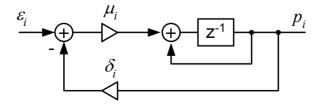

| 7-10.          | Parameter estimation using LMS loops.                                                                                          | 88           |

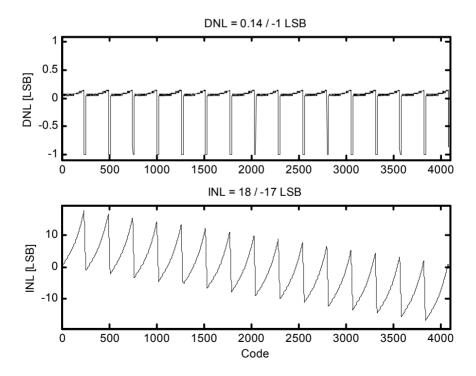

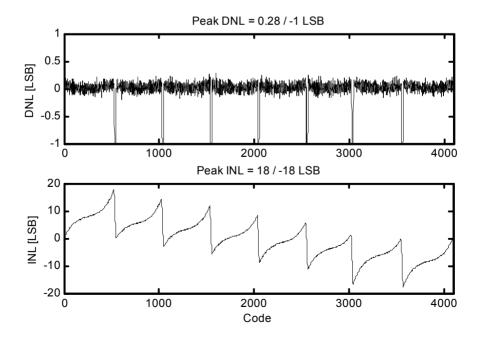

| 7-11.          | DNL and INL without correction ( <i>RNG</i> =0).                                                                               | 91           |

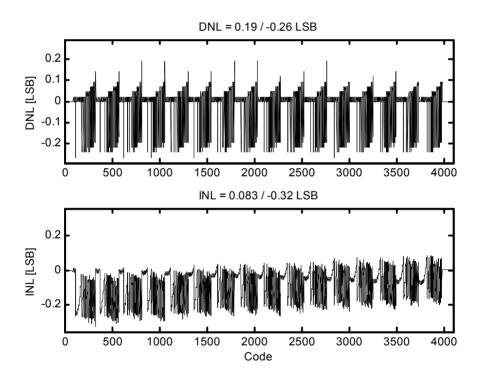

| 7-12.          | DNL and INL with perfectly adjusted calibration parameters ( <i>RNG</i> =0).                                                   | 92           |

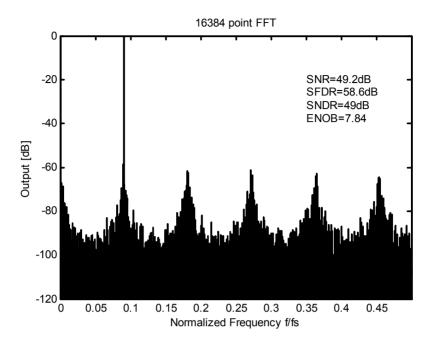

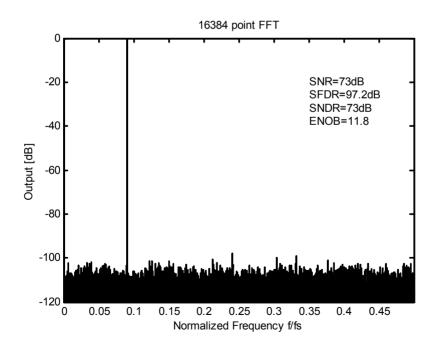

| 7-13.          | FFT without correction ( <i>RNG</i> =0).                                                                                       | 93           |

| 7-14.          | FFT with perfectly adjusted correction parameters ( <i>RNG</i> =0).                                                            | 93           |

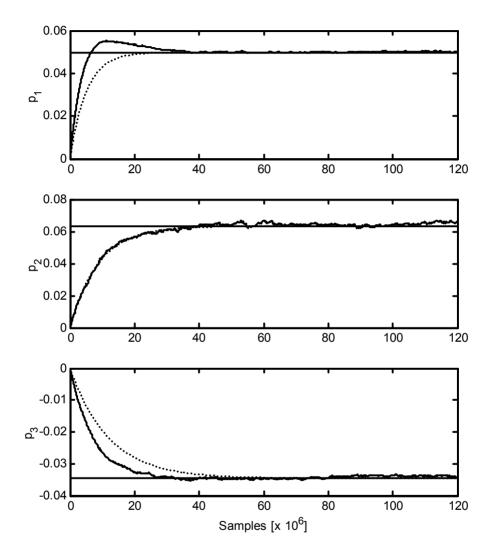

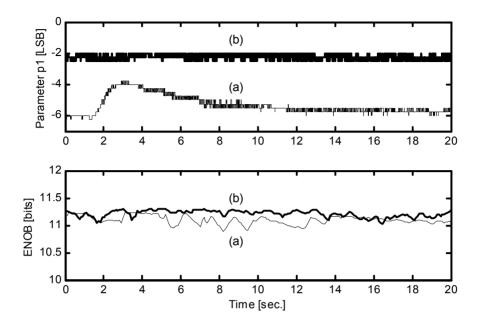

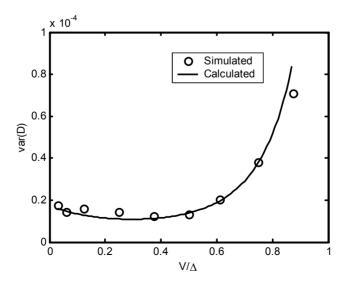

| 7-15.          | Parameter convergence (dotted lines show the expected envelope).                                                               | 95           |

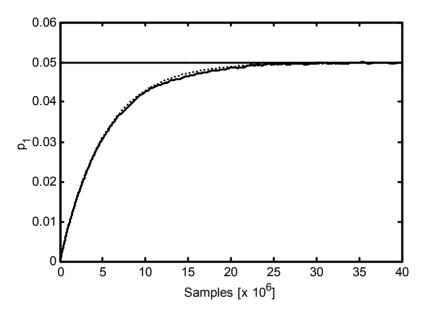

| 7-16.          | $p_1$ convergence with $p_2$ and $p_3$ in steady state.                                                                        | 95<br>96     |

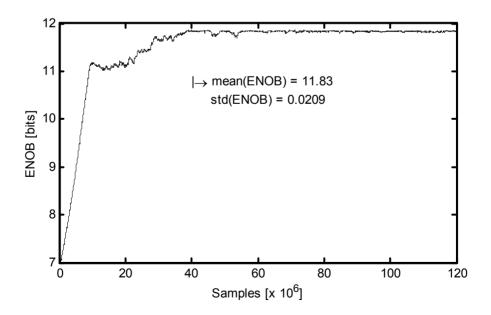

| 7-17.          | ENOB convergence. ENOB convergence.                                                                                            | - 96<br>- 96 |

| 7-17.<br>7-18. | ENOB distribution in steady state.                                                                                             | 90<br>97     |

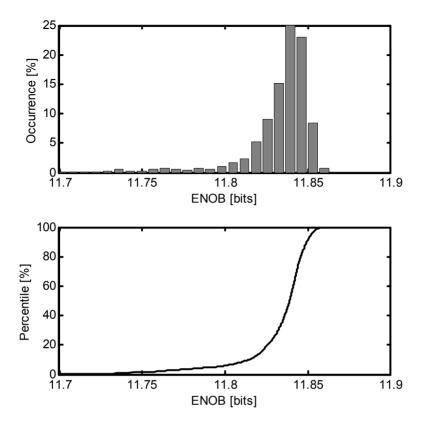

| <i>8-1</i> .   | Prototype architecture.                                                                                                        | 102          |

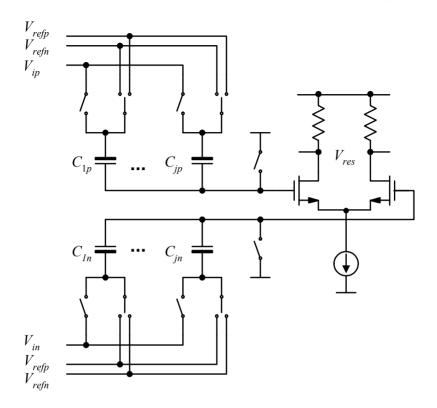

| <i>8-2</i> .   | Stage 1 implementation.                                                                                                        | 102          |

| 8-3.           | Stage 1 residue plot.                                                                                                          | 103          |

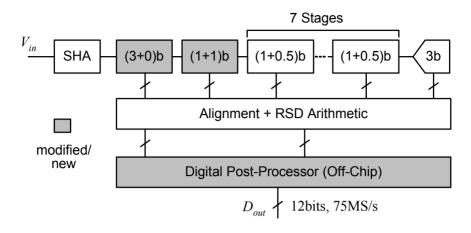

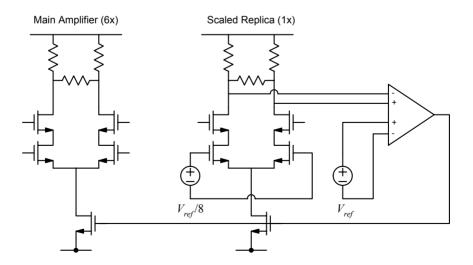

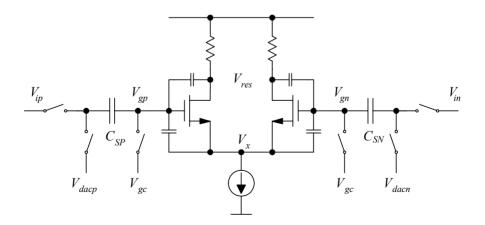

| <i>8-4</i> .   | Replica biasing.                                                                                                               | 105          |

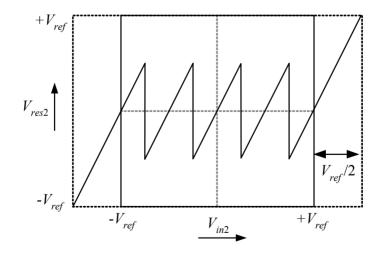

| 8-5.           | Stage 2 residue plot.                                                                                                          | 104          |

| 8-6.           | ADC-FPGA interface.                                                                                                            | 107          |

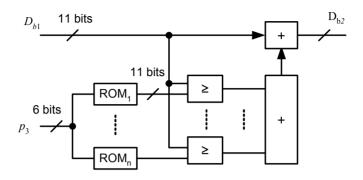

| <i>8-7</i> .   | Incremental error look-up for cubic nonlinearity correction.                                                                   | 108          |

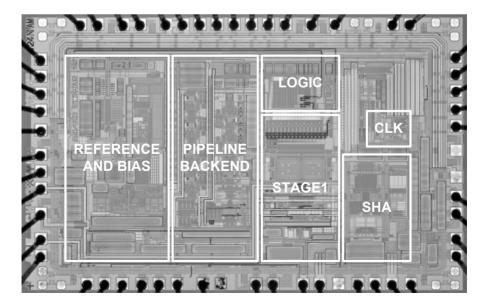

| 9-1.           | Die micrograph.                                                                                                                | 109          |

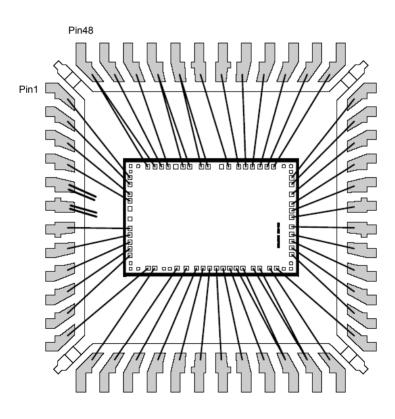

| <i>9-2</i> .   | Bonding diagram.                                                                                                               | 110          |

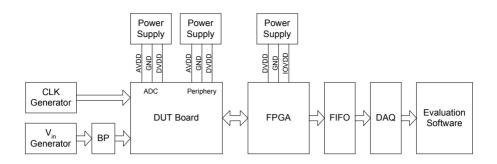

| 9-3.           | Test setup.                                                                                                                    | 112          |

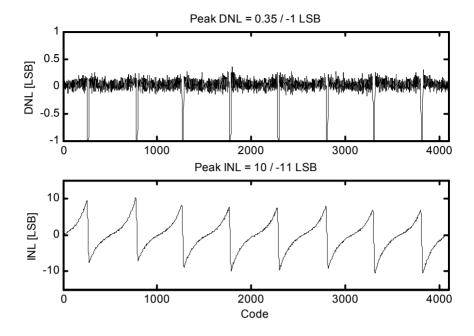

| 9-4.           | Measured nonlinearity without calibration, <i>RNG</i> =0.                                                                      | 113          |

| 9-5.           | Measured nonlinearity without calibration, <i>RNG</i> =1.                                                                      | 113          |

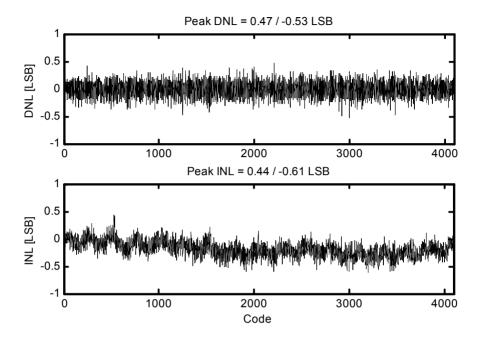

| 9-6.           | Measured nonlinearity with calibration.                                                                                        | 114          |

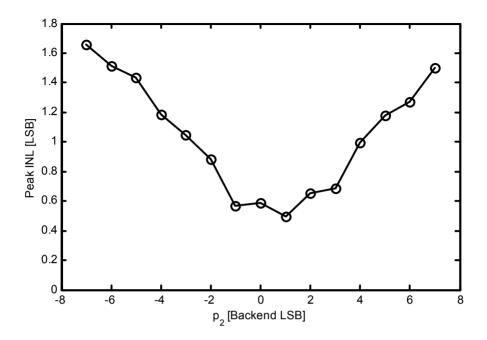

| 9-7.           | Peak INL as a function of correction parameter $p_2$ .                                                                         | 115          |

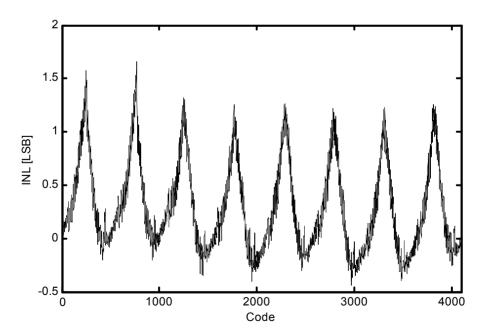

| 9-8.           | INL with $p_2$ =-7 LSB.                                                                                                        | 115          |

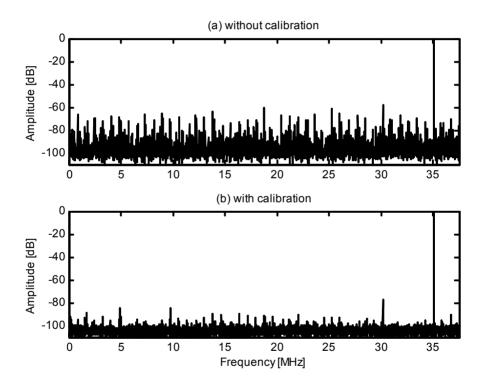

| 9-9.           | Measured output spectrum (4096 point FFT).                                                                                     | 116          |

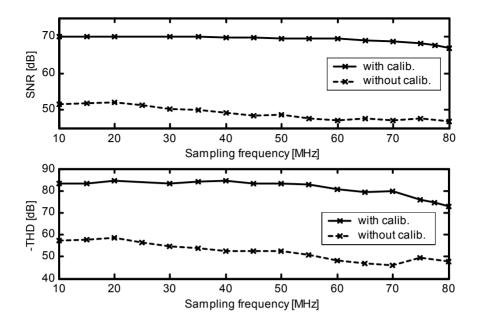

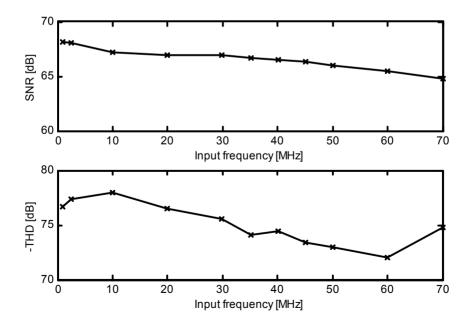

| <i>9-10</i> .  | Noise and distortion performance versus sampling frequency $(f_{in}=1 \text{MHz})$ .                                           | 117          |

| <b>9-</b> 11.  | Noise and distortion performance versus input frequency                                                                        | 117          |

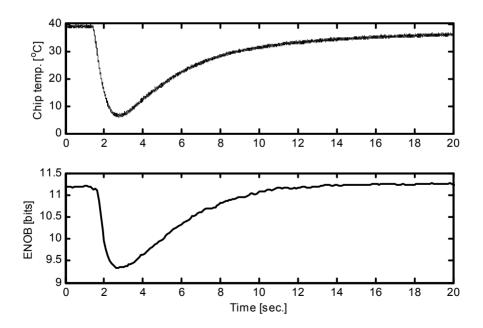

| 9-12.          | $(f_s=75$ MHz).<br>Measured temperature transient. Constant tail bias and LMS                                                  |              |

| 0.12           | loops disabled ( $\mu_1 = \mu_3 = 0$ ).                                                                                        | 118          |

| 9-13.          | Measured temperature transient with active LMS loops:<br>(a) constant tail bias current, (b) with replica bias.                | 119          |

| 120 |

|-----|

| 1   |

| 122 |

| 128 |

| 128 |

| 135 |

| 137 |

|     |

# List of Tables

| 2.1.         | Moore's Law: Integration density in lead microprocessors. | 6   |

|--------------|-----------------------------------------------------------|-----|

| 2.2.         | Speed in lead microprocessors.                            | 6   |

| 2.3.         | Digital energy/power efficiency.                          | 7   |

| 3-1.         | 6-bit Flash ADC Performance.                              | 32  |

| <i>4-1</i> . | Amplifier performance metrics.                            | 47  |

| 7-1.         | Open-loop amplifier parameters.                           | 91  |

| <i>7-2</i> . | LMS Loop Parameters (N=30,000).                           | 94  |

| <i>9-1</i> . | Pinout.                                                   | 111 |

| <i>9-2</i> . | Test equipment.                                           | 112 |

| <i>9-3</i> . | Performance summary (25°C).                               | 121 |

This page intentionally left blank

# Acknowledgments

The authors would like to acknowledge Dimitrios Katsis, Mike Scott, Philip Stark and Sotirios Limotyrakis for their help in improving the manuscript. The authors thank Analog Devices for providing their ADC design for re-use as an experimental prototype. The help of Katsu Nakamura, Sudhir Korrapati, Dan Kelly, Larry Singer, Will Yang and other members of the High-Speed Converter group was greatly appreciated.

This research was funded by Analog Devices and UC MICRO 01-006.

This page intentionally left blank

# Preface

The continued reduction of integrated circuit feature sizes and commensurate improvements in device performance are fueling the progress to higher functionality and new application areas. For example, over the last 15 years, the performance of microprocessors has increased 1000 times. Analog circuit performance has also improved, albeit at a slower pace. For example, over the same period the speed/resolution figure-of-merit of analog-to-digital converters improved by only a factor 10.

Of the many reasons for this disparity between analog and digital circuit performance advances, accuracy requirements stand out as a critical constraint in most analog circuits while being virtually absent in digital designs. Thermal noise, linearity, and matching are distinctly analog circuit problems and require design tradeoffs that invariably lower achievable performance. For example, linearity requirements are usually met with highgain feedback loops. Unfortunately, this solution also lowers circuit speed and results in elevated noise, reduced signal range, and increased power dissipation.

Technology scaling, while unquestionably advantageous for digital circuits, further exacerbates analog circuit design challenges. While offering increased speed, scaled devices suffer from reduced intrinsic gain, further adding to the design challenge of high-gain feedback loops. Reduced supply voltages lower the ratio of useful signal range to supply, leading to increased power dissipation in noise-limited circuits.

A large range of solutions to overcome these challenges is available to designers, both at the technology and circuits level. At the process level they include high supply options and a choice of transistor threshold voltages. Circuit innovations consist of gain boosting and nested Miller compensation.

xx

While extending the feasibility of analog circuits in scaled technologies with low supply voltages, these techniques come at the cost of a combination of increased process complexity, reduced performance, and added power dissipation.

This book proposes a different approach that takes advantage of the availability of high performance digital processing to relax analog circuit linearity requirements. The use of simple but nonlinear open loop amplification translates into increased analog circuit performance or lower power dissipation. In a careful design that uses a modern process, the area and power penalty of the added digital circuitry is negligible and benefits fully from further technology scaling.

Performance demands and design challenges for analog circuits will continue to increase in the future. This book gives the designer a powerful new tool to meet these demands.

Bernhard E. Boser Berkeley, January 2004

# Chapter 1 INTRODUCTION

### 1. MOTIVATION

Enabled by the continuing aggressive scaling of fine line integrated circuit technology, digital signal processing (DSP) and computing have become the main progress drivers in modern electronic systems. With decreasing transistor dimensions, binary computations are performed at lower energy levels and higher speed, resulting in an increasing number of highly sophisticated architectures and algorithms that can be efficiently implemented using digital electronic circuits. In the past decades, this development has led to a continuous doubling of microprocessor performance every 18 months [1].

While purely analog circuits can also benefit from technology scaling, several limitations account for relatively slow performance improvements over time. Most fundamentally, the simultaneous requirement of high speed, low distortion and low noise in the processing of analog signals often translates into poor power efficiency and limited throughput. Furthermore, decreasing supply voltages and reduced intrinsic transistor gain in modern technologies make the design of highly linear, high dynamic range analog building blocks an increasingly challenging task [2].

As a result of these trends, designers lean toward a system partition with a minimum number of virtually unavoidable analog components. Among them is the analog-to-digital converter (ADC), which is required to interface digital processors to "real life" signals such as radio, image and speech waveforms. Since quantization of continuous amplitude information requires analog operations, ADCs often limit the throughput of DSP based systems. In addition, the fairly high power consumption of today's converters is also becoming an increasingly severe showstopper. Especially in applications requiring portability, the operating speed of ADCs tends to be set by the allowable power dissipation, rather than the technological limit.

# 2. OVERVIEW

This book is concerned with improving the speed and power efficiency of analog-to-digital converters. In particular, we explore the opportunity to overcome analog circuit limitations by incorporating digital domain algorithms into the conversion process. The proposed "digitally assisted" converter makes extensive use of the dense, low cost and low power DSP circuitry available in modern integrated circuit technology.

In recent years, the pipelined ADC in Complementary Metal-Oxide-Silicon (CMOS) technology has become the most popular architecture for high speed Nyquist conversion at medium resolutions of 8-14 bits and conversion speeds ranging from 1-200 Mega-Samples per second (MS/s). Typical applications include radio receivers and base stations, digital imaging and video, ultra-sound, radar and sonar systems.

In this book, the pipelined ADC topology is used as a vehicle to derive and demonstrate an alternative approach to conventional quantizers that rely on accurate analog signal processing. By delegating many of the precision requirements from the analog to the digital domain, the proposed converter can benefit from technology scaling rather than being impeded by its limitations.

Among the key building blocks in pipelined ADCs are the residue amplifiers that interface successive converter stages. Especially in the converter front-end, these gain elements have to meet very stringent speed, noise and linearity specifications and therefore tend to set the overall power dissipation and attainable speed.

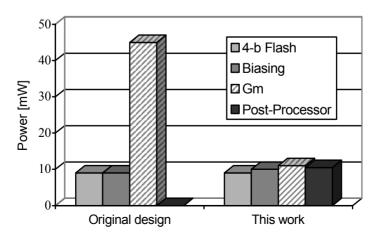

The key feature of this research is a DSP driven technique that alleviates linearity requirements in the analog signal path and thereby helps to break the classical speed-noise-linearity constraint loop. Traditional precision feedback amplifiers are replaced by simple open-loop structures that exhibit superior speed, power efficiency and improved immunity to technology scaling. In the presented proof-of-concept prototype, this approach enables power savings of up to 75% in critical sub-circuits.

Figure 1-1 shows a block diagram of the digitally assisted ADC. A digital post-processor takes the raw, imprecise conversion result and performs the task of identifying and compensating analog domain nonidealities, including mismatch errors and amplifier nonlinearity. In the described converter, the system identification process is based on the

#### INTRODUCTION

evaluation of the raw code signal statistics, and "blind" in the sense that no precise test signal is superimposed or injected into the analog signal path. The linearization parameters are continuously updated during normal ADC operation to track variations in operating conditions such as temperature and supply voltage.

Digital correction and calibration of analog domain non-idealities is not new. Especially in pipelined ADCs, digital correction [3] and calibration [4] have been used extensively to overcome offset and unit element mismatch errors. However, the characteristic feature of the approach demonstrated here is the extent to which digital compensation is used. Treating distortion in semiconductor circuits as a digital domain problem is the main contribution of this work.

Even though the solution presented is tailored for a specific architecture, most of the general concepts and paradigms can form the basis for similar approaches involving other circuit topologies. Some examples of derivative strategies are summarized in chapter 10.

Figure 1-1. System overview.

# **3. CHAPTER ORGANIZATION**

This book is divided into ten chapters. Chapter 2 reviews ADC figuresof-merit and presents a motivating survey of the trends and impact of technology scaling on ADC performance. It shows that the computing capabilities of digital circuits have outpaced progress in analog-to-digital conversion interfaces by more than two orders of magnitude in the past 15 years.

Chapter 3 revisits the controversial question of the impact of scaling on analog circuit power efficiency, and provides a correction to previous, pessimistic analyses.

Chapter 4 aims to identify opportunities for improving the power efficiency in ADCs. The cost for precise and linear analog signal amplification in terms of power efficiency is evaluated, and serves as the main motivation for the modified, open loop pipelined ADCs discussed in chapter 5.

Chapters 6 and 7 describe the proposed digital post-processing mechanism that compensates for linear and nonlinear pipeline stage nonidealities. The two main elements of the developed scheme are a redundancy-based digital correction mechanism and a statistics based background calibration technique.

Chapter 8 details the implementation of a 12-bit 75 MS/s pipelined ADC [5] that was used to evaluate the proposed concepts. Detailed measurement results confirming the feasibility of the digitally assisted ADC concept are illustrated in chapter 9. Highlights of these results include the digital reduction of the converter's integral nonlinearity error from 18 to less than 0.7 least significant bits (LSBs).

Chapter 10 contains a summary of this book and presents a proposal for future research and development.

# Chapter 2

# **PERFORMANCE TRENDS**

### **1. INTRODUCTION**

In the past decades, "Moore's Law" [6] has governed the revolution in microelectronics. Through continuous advancements in device and fabrication technology, the industry has maintained exponential progress rates in transistor miniaturization and integration density. As a result, microchips have become cheaper, faster, more complex and power efficient.

This chapter surveys the impact of technology scaling on the performance of digital circuits and analog-to-digital interfaces; the focus is placed on the past 15 years, during which CMOS technology has been the most popular technology for a large number of applications.

As shown in the following sections, digital performance metrics have grown faster than relevant metrics in ADCs. The resulting large and growing performance gap is the motivation of this research towards a more "digitally assisted" conversion interface.

In the context of the presented data, it should be noted that an objective comparison of absolute performance metrics over time is difficult. Benchmarks in electronic systems are usually expressed using "figures of merit" that lump several performance characteristics into one number. Finding and assigning an appropriate weight to each of the contributing aspects is challenging, subjective and context dependent. For instance, the trend towards portable, battery-operated equipment has led to a shift in paradigms toward power efficient systems, resulting in a change of constraints and goals over time. This comparative survey aims to illustrate only orders of magnitude in relative performance improvement over time and avoids such second order considerations.

### 2. DIGITAL PERFORMANCE TRENDS

Digital circuit applications can be regarded as the main driver for semiconductor device scaling. Historically, the development of new CMOS technology generations has been primarily motivated by the rapidly growing demand for high performance in digital microprocessors. Smaller feature sizes result in faster transistor switching speeds and lower energy consumption per binary transition.

While it is clear that technology scaling must eventually come to an end, the current roadmap of the Semiconductor Industry Association (SIA) foresees a continuation of the above trend up until the year 2016, when the physical transistor gate length is expected to reach 9nm [7]. Table 2.1 summarizes the progress in feature size and integration density over the past 15 years [1].

|                                        | 1987       | 2002         | Rate of Change        |

|----------------------------------------|------------|--------------|-----------------------|

| Transistor Gate<br>Length ( <i>L</i> ) | 1 µm       | 0.13 μm      | 0.5x every<br>5 years |

| Transistors/Die                        | ≅1 Million | ≅100 Million | 2x every<br>2.3 years |

Table 2.1. Moore's Law: Integration density in lead microprocessors

### 2.1 Microprocessor Speed

The attainable speed in digital circuits is approximately proportional to the technology feature size. A widely accepted figure of merit for digital circuit speed is the so-called "fan-out of four" (*FO*4) delay [8]. As illustrated in Table 2.2, this metric has been continuously reduced by a factor of two every 5 years, which coincides with the rate of feature size reduction in technology.

|                         | 1987   | 2002    | Rate of Change |

|-------------------------|--------|---------|----------------|

| Delay (FO4)             | 260mg  | 17mg    | 0.5x every     |

| ≅360ps· <i>L/µm</i> [9] | 360ps  | 47ps    | 5 years        |

| Clock Speed             | 20MHz  | 1.7GHz  | 2x every       |

| Clock Speed             | ZUMITZ | 1./UHZ  | 2.3 years      |

| SPECInt 2000            | ~1     | ~1000   | 2x every       |

| Performance             | ≅1     | ≅1000   | 1.5 years      |

| MIPS Performance        | ~10    | ~10.000 | 2x every       |

| wiips periormance       | ≅10    | ≅10,000 | 1.5 years      |

Table 2.2. Speed in lead microprocessors.

Aside from this raw speed improvement, designers have managed to achieve further performance enhancements both by refining logic gate topologies and by increasing the level of pipelining. Pipelining reduces the number of gate delays between registers and thus improves system throughput. As a result of these factors, clock speed in lead microprocessors has doubled approximately every 2.3 years. This growth is more than twice that of *FO*4 delay.

An additional advantage in microprocessors that adds to the overall computing power is the extensive amount of parallelism feasible in fine line technologies. On top of the quickly growing clock speed, architectural parallelism has led to a net doubling of computing power every 1.5 years. Quantifying the computing power of a microprocessor objectively is difficult and controversial [10]. However, both the hardware-oriented "MIPS" metric and the more accepted computing measure "SPECInt" show this tremendous growth rate (see Table 2.2) [11].

## 2.2 Microprocessor Power Efficiency

Feature size scaling has decreased the energy per logic transition by 65% in each technology generation [12]. Equivalently, this corresponds to an energy reduction by a factor of two every 1.7 years. This dramatic rate of improvement stems from both smaller capacitance and lower supply voltage, which has quadratic impact on energy.

For high performance microprocessors, however, this advantage is offset by the extra effort spent on pipelining and architectural parallelism to boost computing power. As a result, the power efficiency of lead microprocessors, measured in mW/MIPS has decreased only by about 40% per technology generation (see *Table 2.3*).

|                                           | 1987           | 2002                | Rate of Change |

|-------------------------------------------|----------------|---------------------|----------------|

| Relative Energy per                       | 1              | $1.8 \cdot 10^{-3}$ | 0.5x every     |

| Transition ( $\propto C_{ox}V_{DD}^{2}$ ) | 1              | 1.8.10              | 1.7 years      |

| Lead Microprocessor                       | 200mW/MIPS     | 10mW/MIPS           | 0.5x every     |

| Power Efficiency                          | 2001110/101115 | 10111 W/WIFS        | 3.4 years      |

Table 2.3. Digital energy/power efficiency.

### **3. ADC PERFORMANCE TRENDS**

Analog circuits, including ADCs, have also benefited from the technology scaling that is mostly driven by digital applications. Today's

mainstream CMOS technology has proven to be most suitable for costefficient implementation of high-performance data converters, filters and radio frequency transceivers. Recent performance highlights that make ultimate use of the available integration density and speed in CMOS include an 8-bit, 20-GSample/s ADC [13], and 5-GHz transceiver chips for wireless local area networks [14-16].

In the following survey, we will examine the rate of performance growth in ADCs. To capture and compare performance of ADCs, we use a set of commonly used figures of merit. The following section briefly discusses these quantities with respect to their origin and limitations.

## **3.1** ADC Figure of Merit Considerations

The product of conversion bandwidth and number of effective quantization levels represents the most basic performance metric for ADCs [17]. We define this quantity as

$$FOM1 \quad f_s \cdot 2^{ENOB}, \tag{2-1}$$

where  $f_s$  is the sampling rate of the converter and *ENOB* is the effective number of bits given by

$$ENOB \quad \frac{SNDR - 1.76dB}{6.02dB}.$$

(2-2)

Since the signal-to-noise and distortion ratio (*SNDR*) of a converter usually depends on the frequency of the input signal, this figure of merit must include some fixed condition for the frequency at which *ENOB* was measured. Alternatively, it is common to replace the sampling rate  $f_s$  in (2-1) by twice the signal bandwidth for which the peak *ENOB* has dropped by 3dB. This frequency is often referred to as the effective resolution bandwidth (*ERBW*) [17, 18].

A fundamental issue in the figure of merit described by (2-1) lies in the relative weighting of throughput and accuracy. For instance, the expression implies that a 6-bit converter running at 1GS/s is equally "hard to build" as a 7-bit converter that operates at 500MS/s. While there is no fundamental argument that holds up this exact tradeoff, it is well supported in practice. The survey [17] shows that for every octave increase in bandwidth, the attainable resolution of state-of-the-art ADCs tends to drop by approximately one bit.

A second, commonly used figure of merit that includes the power dissipation of the ADC is the "energy per conversion" figure of merit given by [19]

$$FOM2 \quad \frac{P}{f_s \cdot 2^{ENOB}}.$$

(2-3)

Note that contrary to the standard convention used in figures of merit, a smaller value of this metric indicates better performance.

In *FOM*2, the tradeoff between precision and power is controversial. Equation (2-3) suggests that the power consumption of an ADC should double for each added bit. However, assuming that the ADC is limited by kT/C thermal noise, adding an extra bit requires quadrupling the effective capacitance in the converter. This in turn, requires a 4x increase in current and power dissipation to maintain the same speed. Based on this argument, some authors use a figure of merit in which the denominator carries the precision as  $2^{2ENOB}$ . In practice, this modification is overly pessimistic, since almost never all power dissipating circuits are limited by thermal noise. For improved accuracy, one could introduce a fitting parameter in the denominator, such that

$$FOM2^* \quad \frac{P}{f_s \cdot 2^{c \cdot ENOB}}, \qquad (2-4)$$

where c is a constant that quantifies the tradeoff between power and precision for a specific ADC architecture. Figures of merit of this form have recently been proposed [20]. In practice, however, it turns out that c=1 is a sufficiently good choice to compare ADCs over many technology generations, topologies, speeds and resolutions [17]. As a result, (2-3) has evolved as one of the most widely accepted figure of merits for ADCs.

One way to avoid the problem of uncertainty in the exact powerresolution tradeoff is to compare only converters with approximately the same effective resolution. The corresponding quantity is given by

$$FOM3 \quad \frac{P}{f_s}\Big|_{ENOB\cong fixed}.$$

(2-5)

This figure of merit is most useful when comparing specific implementations of virtually identical converter topologies, e.g. 10-bit

pipelined ADCs. We will use (2-5) in a detailed architecture-specific ADC survey in chapter 3.

In the following sections we use (2-1) and (2-3) for a more general trend survey on the impact of technology scaling on ADCs of all variants.

# **3.2 ADC** Throughput

Figure 2-1 illustrates the trend in ADC throughput since 1987. The performance data for this survey origins from  $[17]^1$ , augmented with additional data from the International Solid-State Conference (ISSCC) from the years 1999-2003. Each data point in Figure 2-1 corresponds to a specific, single ADC reported in the respective year. An exponential fit to all data points from 1987-2003 shows that the ADC *FOM*1 (equation (2-1)) has doubled only every 6.5 years. A fit to only the peak performance data points in each year yields a slightly faster progress rate of doubling every 4.7 years.

This difference in slopes may be due to the fact that many ADCs are not optimized for peak throughput alone, but also for good power efficiency or other application-specific constraints. Nevertheless, the slow improvement of the peak performance indicates that the progress in conversion interfaces has been lagging that of purely digital circuits discussed in section 2.

Figure 2-1. ADC performance trend.

<sup>1</sup> ADCs using cooled, superconducting devices have been excluded here.

# **3.3 ADC Energy Efficiency**

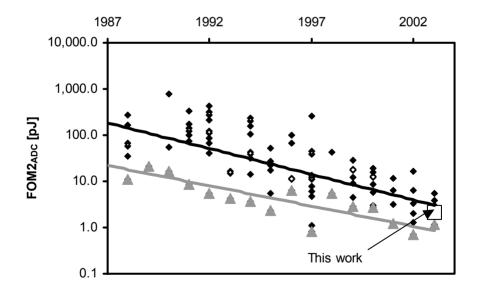

Using the same source data as in section 3.2, Figure 2-2 shows the development of the energy per conversion figure of merit (equation (2-3)) over time. Again, we perform two distinct fits to the scatter plot. Taking all ADCs into account, *FOM*2 has halved every 2.7 years since 1987, leading to a current state-of-the art value of roughly 3pJ per conversion.

A fit to only the lowest energy parts in each year shows slightly slower progress (0.5x every 3.4 years). This difference in progress rates between low energy and mainstream ADCs may be due to a general emphasis on low power systems in the 1990s.

### **3.4** Trend Comparison

It is now interesting to compare the advancements in ADCs to those of digital circuits on a relative scale. Figure 2-3 illustrates the divergence in attainable speed between the two domains.

As explained in section 2.1, microprocessors benefited from the raw improvement in technology speed, and also from aggressively increasing parallelism. The resulting steep progress rate of performance doubling every 1.5 years has created a performance gap of 150x between digital computing power and ADC speed.

Figure 2-2. ADC energy efficiency trend.

Figure 2-3. Comparison of speed trends: ADCs versus digital.

The situation for energy efficiency is similar. As shown in Figure 2-4, the energy efficiency of logic gates has outperformed the energy per conversion in ADCs by a factor of 14.

Figure 2-4. Comparison of energy efficiency trends: ADCs versus digital.

It is interesting to note, however, that the overall energy efficiency of lead microprocessors has not improved as fast as that of ADCs. For performance-optimized lead microprocessors, the intrinsic progress in logic gate efficiency is offset by the overhead from architectural parallelism.

Despite this fact, it is clear that there exists a large and growing gap between analog and digital capabilities. Leaving the architectural growth component aside, progress in logic circuits has outpaced ADCs by about 12x in speed ( $f_{CLK}$  in Figure 2-3) and 14x in energy efficiency.

To an increasing extent, data converters are the bottleneck of many systems both for throughput and power dissipation. As an example, Figure 2-5 shows a typical mixed-signal application in which both the ADC and digital signal processing backend, consisting of roughly one million logic gates, have been integrated on the same chip. Interestingly, as typical in such applications, the ADC portion (upper right corner) occupies only a small fraction of the die area but consumes more than 50% of the total system power.

Power inefficiency has become one of the most severe showstoppers in the application of ADCs. In many cases, the throughput of ADCs is set by the allowable power dissipation. Figure 2-6 shows several ADC application regimes in the speed/resolution space with contours of equal power consumption.

Figure 2-5. Modern ADC application: 802.11 base band processor for wireless networks [21].

With the increasing trend towards battery-powered devices, the power budget of an ADC is usually limited to a fraction of a Watt. As we see from Figure 2-6, this dictates a very strict upper limit in performance that is independent of technology limits.

The large and growing gap between ADC performance and power efficiency, compared with the capabilities of low-power digital devices poses the main motivating question behind this research: How can we use digital circuits to boost the figure of merit in conversion interfaces? The potential advantage of increased "digital assistance" in converters has been recognized and documented in numerous recent publications on the subject (e.g. [22-28]). However, most of the proposed schemes have not yet delivered a significant advantage over "purely analog," optimized ADCs.

*Figure 2-6.* ADC applications in the speed/resolution space. The equi-power contours assume *FOM2*=3pJ/conversion.

# Chapter 3

# SCALING ANALYSIS

# **1. INTRODUCTION**

For many analog building blocks, including ADCs, it is not clear how power efficiency changes as a function of implementation feature size. Some previously published analyses suggest that there is a detrimental price for implementing high dynamic range functions in a low voltage, deep submicron technology [29, 30]. Based on these analyses, the energy figure of merit is bound to deteriorate in fine-line, low-voltage technologies. However, as we have seen in the previous chapter, the migration to finer line widths has not yet caused a reduction in the energy efficiency of ADCs.

The following analysis revisits the controversy over the impact of scaling on analog circuits. The study combines first- and second-order circuit effects and survey data to yield a more refined view that helps explain the trends seen in the previous chapter. The investigation contains three parts:

- A brief summary of CMOS device scaling. How and why are technology parameters varied as channel length decreases?

- Identification and scaling analysis of transistor performance metrics that are important for analog circuits.

- An investigation of how scaling of transistor metrics affects the power efficiency of analog circuits. Here, we distinguish between "matchinglimited" and "noise-limited circuits," and focus on representative building blocks of flash- and pipelined ADCs respectively.

# 2. BASIC DEVICE SCALING FROM A DIGITAL PERSPECTIVE

From a digital circuit perspective, MOS transistors have been scaled continuously to achieve: (1) higher integration density and reduced cost, (2) higher speed, and (3) lower power consumption. These goals are met by following certain scaling guidelines, which, to first order, have two independent variables: the minimum device feature size, and the supply voltage ( $V_{DD}$ ).

As explained in [31], the so-called "full scaling approach" attempts to keep electrical fields in the device constant by scaling both voltages and physical dimensions equally. This scaling approach effectively achieves the three scaling goals mentioned above. In practice, however, constant field scaling is not feasible since built-in potentials and the sub-threshold slope (set by kT/q) do not scale with transistor dimensions. Therefore, some form of "general scaling" is usually needed. In this approach, voltages and geometries are reduced by slightly different scaling factors. For each technology generation, the scaling parameters are chosen with the primary objective of maximizing the performance improvement over the previous generation.

One consequence of the general scaling approach, however, is that robustness and reliability tend to trade-off with attainable performance. Some of the resulting issues are:

- Active power density is steadily rising due to slower  $V_{DD}$  scaling relative to dimension scaling.

- Transistor threshold voltages ( $V_{TH}$ ) must be scaled down with  $V_{DD}$  to prevent performance loss [31]. However, leakage currents increase roughly 10x for every 100mV drop in  $V_{TH}$ . This translates into the inability to effectively turn off the device. A minimum allowable  $V_{TH}$  of about 0.2V is expected [32].

- Increased sensitivity to interconnect parasitics. The RC delay of wires has been scaling much slower than device delays [31]. Better interconnect material (e.g. Copper) and improved circuit-level routing solutions have become necessary.

Despite the challenges above, digital circuits are expected to benefit from scaling CMOS technology for at least another five years. Conservative estimates predict that the energy per logic transition will continue to drop until the channel length reaches about 40nm [32].

# 3. TECHNOLOGY METRICS FOR ANALOG CIRCUITS

Performance metrics for a given technology can be divided into analog and digital parameters. While a digital circuit designer might care mostly about a technology's ring oscillator frequency and energy per logic transition, these parameters have no direct meaning in the context of analog circuits.

In the following sections, we summarize important technology performance parameters from the viewpoint of an analog circuit designer and examine their change with technology scaling. We use qualitative arguments and simulation data from BSIM3v3 models [33] to quantify scaling behavior. Most of the underlying device models were obtained from the MOSIS foundry service web site [34]. For brevity, we restrict the study to four representative technology nodes at  $0.5\mu$ m,  $0.35\mu$ m,  $0.25\mu$ m and  $0.18\mu$ m. These generations span roughly 7.5 years on the scaling roadmap and are sufficient to predict and analyze general trends.

# 3.1 Supply Voltage

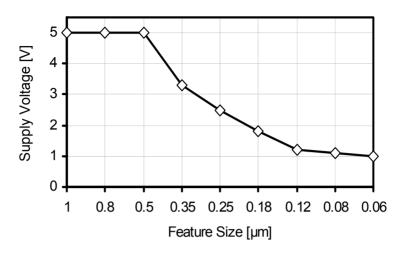

Signal headroom plays an important role in the design of analog circuits. As supply voltages decrease as dictated by the general scaling approach, many analog functions become harder to implement. For instance, with reduced headroom, it may no longer be feasible to stack transistors in cascode configuration to achieve high output impedance and gain (see e.g. [30]). Another detrimental factor is the achievable dynamic range of the circuit. As the available signal swing scales down by U, noise power in the circuit must be reduced by  $U^2$  to maintain a given dynamic range. This effect is important in noise-limited analog circuits, which are analyzed in more detail in section 5. For further comparison and figure of merit calculations, we use supply voltages from the current and previous technology scaling roadmaps [7] (see Figure 3-1). Over the four technology nodes of interest, supply voltages have been reduced from 5V (0.5µm) to 1.8V (0.18µm).

Figure 3-1. Supply voltage scaling.

# **3.2** Transit Frequency

The transit frequency  $(f_T)$  can be regarded as a small-signal, high frequency figure of merit for transistors. At the operating frequency  $f=f_T$ , a transistor is defined to have unity current gain in a common source configuration with shorted drain. Therefore,

$$f_T = \frac{1}{2\pi} \frac{g_m}{C_{gs} + C_{gd}},$$

(3-1)

where  $g_m$  is the device's transconductance and  $C_{gs}$  and  $C_{gd}$  are its gate-source and gate-drain capacitances, respectively. Assuming square law models (see e.g. [35]),  $f_T$  is related to device parameters by

$$f_T \cong \frac{1}{2\pi} \frac{\mu \cdot V_{OV}}{L^2},\tag{3-2}$$

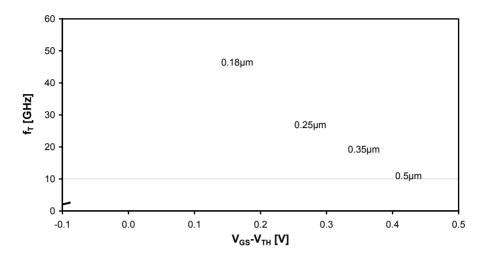

where  $\mu$  is the channel mobility and  $V_{OV}$  is the gate overdrive  $V_{GS}$ - $V_{TH}$  of the transistor. Due to short-channel effects such as mobility degradation and velocity saturation,  $f_T$  tends to scale by a factor of less than  $1/L^2$ . Figure 3-2 shows simulation data of NMOS transit frequency for minimum length devices in different technologies versus gate overdrive voltage  $V_{OV}$ .

Figure 3-2. NMOS transit frequency.

As we argue later, the available device  $f_T$  can be directly related to analog building block bandwidth and is therefore an important metric in deriving figures of merit for analog circuit purposes. As opposed to the drastic drop in supply voltage, availability of transit frequencies approaching 100GHz is a welcome feature for cutting edge analog designs and enables pushing the operating speed.

# **3.3** Transconductor Efficiency

The transconductor efficiency  $g_m/I_D$  quantifies the available device transconductance per current invested. For a square law transistor model,  $g_m/I_D$  is given by

$$\eta \quad \frac{g_m}{I_D} \quad \frac{2}{V_{OV}}.$$

(3-3)

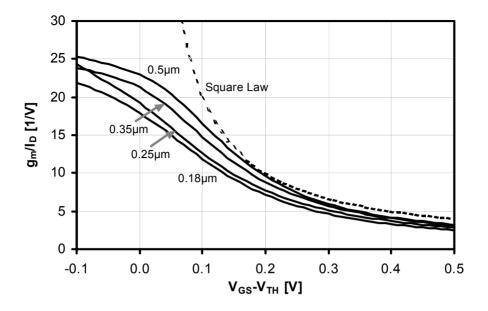

For practical devices,  $\eta$  is always below the ideal value predicted by (3-3). For very small gate overdrive  $V_{OV}$  (<50mV), the device enters a region close to bipolar operation and  $g_m/I_D$  is bounded by the value  $1/(n \cdot kT/q)$ , where *n* is the transistor's sub-threshold slope factor [36]. For large gate overdrive, velocity saturation and mobility degradation cause  $g_m/I_D$  to be about 10-20% below the square law estimate. Figure 3-3 shows the transconductor efficiency for the technologies considered here.

*Figure 3-3.* Transconductor efficiency versus gate overdrive. The dotted line shows the case for perfect square law devices.

The 0.18µm technology shows the lowest  $g_m/I_D$  in all operating regions. This is due to the fact that this technology exhibits the largest sub-threshold slope factor and suffers most from short-channel effects. In future technology generations, enhancements such as strained silicon [37] may help reduce the relative impact of this penalty.

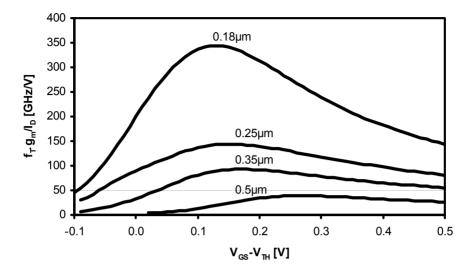

From the perspective of analog circuit design, it is interesting to plot the product of transconductor efficiency and transit frequency. To some degree, this quantity captures the fundamental tradeoff between speed and power and helps to identify reasonable operating regimes for analog transistors. Figure 3-4 shows a plot for the technologies under consideration.

For most technologies, the optimal biasing, i.e. the maximum of  $g_m/I_D:f_T$  occurs close to a gate overdrive voltage of 150-200mV. It is interesting to note that the peak is at lower gate overdrive for smaller gate lengths. This trend is explained by the effect of mobility reduction due to increasing vertical electric fields in smaller feature sizes [36].

*Figure 3-4.* Product  $g_m/I_D \cdot f_T$ .

# 3.4 Intrinsic Gain

In solid-state transistors, the relationship between control node voltage and device current is highly nonlinear. Linear gain elements are therefore typically implemented using electronic feedback. With feedback, nonlinearities are attenuated by the circuit's loop gain T. In most amplifier configurations, T is given by a product of individual intrinsic transistor gains  $(g_m \cdot r_o)$ . With decreasing transistor geometries, the intrinsic device gain decreases, which makes it harder to meet minimum loop gain requirements in precision building blocks.

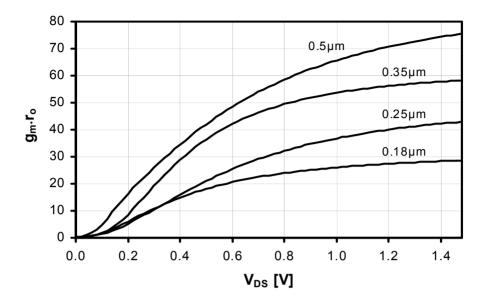

Device physics shows that the decrease in intrinsic gain is due to increased channel length modulation and Drain Induced Barrier Lowering (DIBL) for shorter channels [36]. Figure 3-5 shows intrinsic gain for the different technologies and drain bias for  $V_{OV}$ =200mV. Especially critical in the 0.18µm case is the extremely gentle transition to acceptable gain levels. A drain bias of roughly  $3 \cdot V_{OV}$ =0.6V is required to achieve a device gain of 20. This voltage is a large fraction of the total swing that can be accommodated at  $V_{DD}$ =1.8V. Figure 3-6 shows a zoom into the realistic biasing range that can be allocated in today's designs. Just like decreasing  $V_{DD}$ , the low intrinsic device gain in short channel technologies can be regarded as a dynamic range penalty.

Figure 3-5. NMOS intrinsic device gain at  $V_{OV}$ =200mV (minimum channel length).

Figure 3-6. NMOS intrinsic device gain at V<sub>OV</sub>=200mV (Zoom into typical operating region).

## **3.5** Transistor Matching

Since many analog circuits are based on multiples of supposedly identical devices, matching is often critical. For certain topologies, matching becomes the bottleneck for attainable accuracy. The mismatch of transistor parameters is also affected by technology scaling. This section provides an introduction to basic matching properties, and their scaling trends.

The most widely accepted description of the variation in some parameter *P* between two "identical" rectangular devices was first introduced in [38]

$$\sigma^2 \left( \Delta P \right) \quad \frac{A_P^2}{W \cdot L} + S_P^2 \cdot D^2, \qquad (3-4)$$

where  $A_p$  is an area proportionality constant for parameter P, and  $S_p$  describes the variation in P due to spacing. Once the process-dependent constants  $A_p$  and  $S_p$  have been measured or calculated, this relation can be used to predict matching characteristics of various devices.

Analog circuit designers are normally concerned about transistor current mismatch and/or voltage offset. For a differential transistor pair with identical size and bias, these quantities are given by

$$\frac{\Delta I_D}{I_D} = \frac{\Delta \beta}{\beta} - \frac{g_m}{I_D} \cdot \Delta V_{TH}$$

(3-5)

and

$$\Delta V_{GS} \quad \Delta V_{TH} - \frac{I_D}{g_m} \cdot \frac{\Delta \beta}{\beta},$$

(3-6)

where

$$\beta \quad \mu_{eff} \cdot C_{ox} \cdot W / L \,. \tag{3-7}$$

Due to its random nature, the mismatch is usually described in terms of variance. Using (3-4), the random variations in the threshold voltage and current factor become

$$\operatorname{var}(\Delta V_{TH}) \cong \frac{A_{VTH}^2}{W \cdot L}$$

(3-8)

and

$$\operatorname{var}\left(\frac{\Delta\beta}{\beta}\right) \cong \frac{A_{\beta}^{2}}{W \cdot L}$$

. (3-9)

These expressions neglect distance effects. In practice, this is a very good assumption for device separation below 200µm [39].

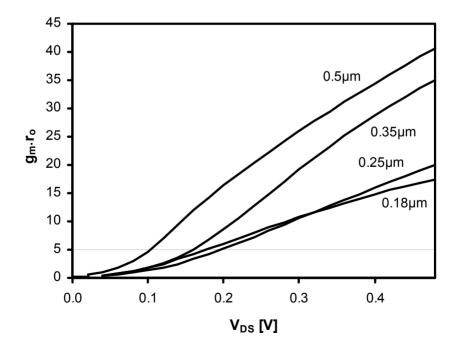

Scaling trends of mismatch can be analyzed by relating fluctuations in device manufacturing to physical device parameters. Threshold voltages are determined mainly by oxide thickness and depletion charge in the channel. Variations in the threshold voltage are caused mostly by the random nature of the ion implantation and diffusion processes, which leave an amount of fixed charges in the depletion region. Assuming that  $V_{TH}$  mismatches are due mainly to these random doping fluctuations, one can show that  $A_{VTH}$  is directly proportional to oxide thickness [40, 41]. As a result, threshold voltage matching improves with technology scaling.

This is confirmed by Figure 3-7, which shows data for six generations of CMOS technology [42]. Unfortunately, as explained in [42],  $A_{\beta}$  tends to remain constant with technology scaling. Although  $\Delta V_{TH}$  has so far been the dominant factor to overall mismatch performance,  $\Delta\beta$  is becoming increasingly important. In fine-line technologies, the two mismatch components can be comparable, and both need to be taken into account.

*Figure 3-7.* Technology scaling trends of  $A_{VTH}$  and  $A_{\beta}$ .

## **3.6** Transistor Noise

In MOS transistors, two significant mechanisms contribute to drain current fluctuations. Flicker noise or 1/*f* noise is present due to trapping and de-trapping effects at the silicon-oxide interface [43]. Since flicker noise is inversely proportional to transistor gate area, this noise component typically increases with technology scaling. Analog building blocks exhibit different levels of sensitivity to flicker noise depending on their function and application. In the wideband circuits discussed in Sections 4 and 5, flicker noise is usually of minor concern.

The second, more fundamental noise source is thermal noise, whose power spectral density is

$$\overline{i_d^2} \quad \gamma \cdot 4kT \cdot g_m \cdot \Delta f \ . \tag{3-10}$$

For long channel devices,  $\gamma=2/3$ . Recent measurement results show that  $\gamma$  is approximately 1 in 0.18µm technology [44]. This additional noise adds another component to the dynamic range penalty of scaled technologies.

# 4. SCALING IMPACT ON MATCHING-LIMITED CIRCUITS

Having identified basic device performance scaling trends, we now relate this data to performance of analog building blocks. The following discussion focuses on basic building blocks that comprise ADCs and distinguishes between "matching-limited" circuits discussed in this section and "noise-limited" circuits considered in section 5.

As an example of a matching-limited circuit we study the impact of scaling on flash ADCs. Due to the low resolutions (~4-8 bits), thermal noise tends to be of minor concern in this architecture. However, to achieve high sampling rates, low complexity circuits and small device areas are imperative. For this reason, device matching typically limits the achievable resolution. Like most data converters, flash ADCs exhibit technology-dependent tradeoffs between speed, accuracy, and power consumption. While technology scaling results in the usual short-channel degradations and reduced supply headroom, matching tends to improve. Hence, it is unclear whether smaller feature sizes produce better or worse performance and power efficiency.

# 4.1 Impact of Mismatch

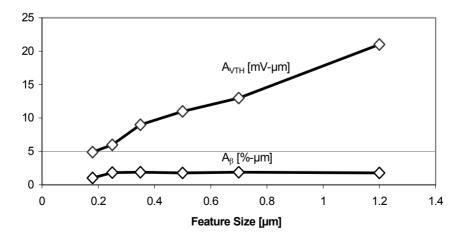

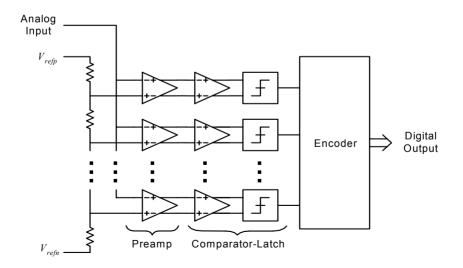

The achievable resolution of Flash ADCs depends on how accurately the analog input can be compared to a set of incremental reference levels. The general topology for a flash ADC is shown in Figure 3-8.

To alleviate offset requirements, a pre-amplifier usually precedes each comparator. As a result, the offset voltage in each signal path tends to be dominated by the differential pair of the pre-amplifier alone. One way to express the offset voltage of a differential pair is

$$V_{OS} \quad \Delta V_{GS} \quad \Delta V_{TH} - \frac{I_D}{g_m} \cdot \frac{\Delta \beta}{\beta}.$$

(3-11)

Equivalently, we may re-write (3-11) in terms of variances

$$\operatorname{var}(V_{OS}) \quad \operatorname{var}(\Delta V_{TH}) + \left(\frac{I_D}{g_m}\right)^2 \operatorname{var}\left(\frac{\Delta\beta}{\beta}\right).$$

(3-12)

Figure 3-8. Flash ADC block diagram.

Substituting (3-8) and (3-9) into (3-12), we obtain

$$\sigma^{2}(V_{OS}) \quad \frac{1}{A_{eff}} \left[ A_{VTH}^{2} + A_{\beta}^{2} \cdot \left( \frac{I_{D}}{g_{m}} \right)^{2} \right], \qquad (3-13)$$

where  $A_{eff}$  is the effective device area,  $W \cdot L$ .

# 4.2 Speed Limitations

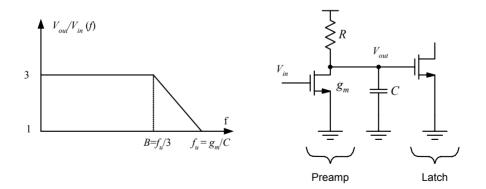

The conversion speed of a flash ADC is limited mainly by the effective bandwidth of the preamp/comparator. Consider the simple model for pre-amplifier/comparator interface shown in Figure 3-9.

Typically, the preamp input stage provides a voltage gain of approximately 3 (or 2-4). The number of time constants needed to reach some settling accuracy is related to the desired resolution. For instance, in a 6-bit ADC we require  $\ln(2^6) \cong 4$  time constants to settle to the desired accuracy. For a given unity gain frequency  $f_u$  in the pre-amplifier, the conversion rate is therefore limited to

$$f_s \cong \frac{f_u}{3 \cdot 4} \quad \frac{f_u}{12} \,. \tag{3-14}$$

Figure 3-9. Preamp/latch model.

# 4.3 **Power-Speed-Accuracy Figure of Merit**

A meaningful metric for converters that are not limited by thermal noise is the power per speed-accuracy figure of merit given by [42]

$$FOM_{PSA} \propto \frac{Power}{Speed \cdot Accuracy^2}$$

. (3-15)

This quantity has units of energy and indicates how much power must be invested at a given conversion rate to achieve a certain (fixed) resolution.

Power consumption is given by

$$Power \propto I_D \cdot V_{DD} \,. \tag{3-16}$$

The expression above implies that the circuits are purely class-A, i.e. continuously biased by constant currents. The amount of digital circuitry in flash topologies varies significantly from one implementation to the next. For simplicity, we neglect digital power consumption in this analysis.

The desired resolution translates into a required accuracy. As we argued above, the attainable accuracy here is limited mainly by mismatch. However, another component that affects the achievable resolution is the reference voltage, which is directly related to the supply voltage. Hence, the accuracy term is

$$Accuracy \propto \frac{r \cdot V_{DD}}{\sigma(V_{OS})},$$

(3-17)

where *r* is the fraction of supply voltage used as the full-scale input range of the converter. For simplicity in this analysis, we assume r=1.

The achievable speed of the converter is given by the bandwidth of the pre-amp input stage driving a comparator latch (see Figure 3-9). The unity-gain bandwidth  $f_u$  is given by

$$f_{u} = \frac{1}{2\pi} \frac{g_{m}}{W \cdot \left(c \cdot L_{\min} \cdot C_{gs}^{'} + C_{db}^{'}\right)},$$

(3-18)

where  $C_{db}$  and  $C_{gs}$  are the drain-to-bulk and gate-to-source junction capacitance per device width. The constant *c* relates the device sizes of the two stages and is specific to the topology used. For simplicity in the

following discussion, we assume c=1. In practice, this is almost never true. However, since c is roughly independent of technology, it can be safely ignored in a relative scaling analysis.

Combining equations (3-15)-(3-18), we obtain

$$FOM_{PSA} \propto \frac{I_D}{g_m} \cdot \frac{\left(L_{\min} \cdot C_{gs}' + C_{db}'\right)}{V_{DD} \cdot L_{\min}} \cdot \left[A_{VT}^2 + A_{\beta}^2 \left(\frac{I_D}{g_m}\right)^2\right].$$

(3-19)

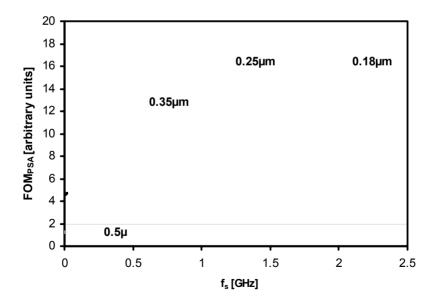

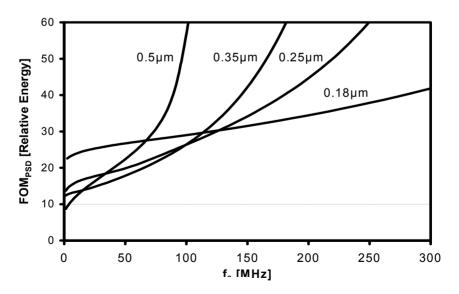

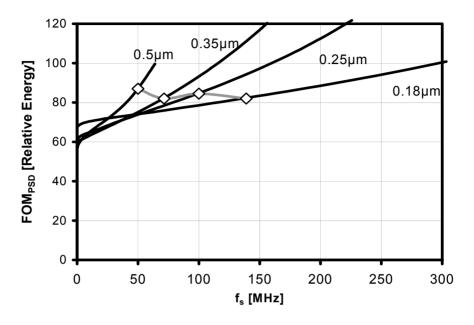

To isolate different mechanisms of technology scaling, we now first assume constant  $A_{VT}$  and  $A_{\beta}$  for each technology. Figure 3-10 shows the resulting  $FOM_{PSA}$  as a function of desired conversion speed  $f_s$ . For this graph,  $g_m/I_D$  and capacitance values are generated using SPICE simulations. A given  $f_s$  determines the required device  $f_T$  and also the maximum  $g_m/I_D$  (see Figures 3-2 and 3-3).

Under the assumption that matching does not improve, Figure 3-10 shows that each technology becomes better than its predecessor only after a certain frequency threshold, beyond which the older generation has insufficient transistor speed. This trend is explained by the fact that both low  $V_{DD}$  and short channels penalize the power through increased accuracy requirements (see (3-19)).

*Figure 3-10.* Flash ADC energy as a function of sampling rate (assuming constant mismatch factors  $A_{VTH}$ , and  $A_{\beta}$ ).

In Figure 3-11, we let the matching coefficients  $A_{VTH}$  and  $A_{\beta}$  scale as described in Section 3. As a result, we now see significant merit in scaling, even for moderate speeds. In contrast to Figure 3-10, Figure 3-11 shows that technologies with smaller feature sizes can achieve simultaneous speed and power efficiency improvements.

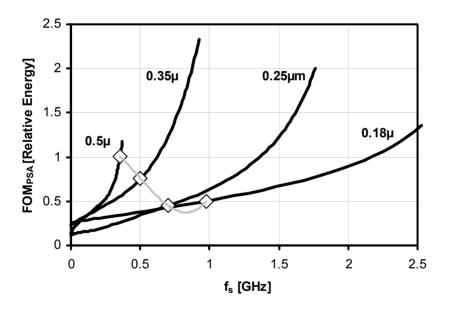

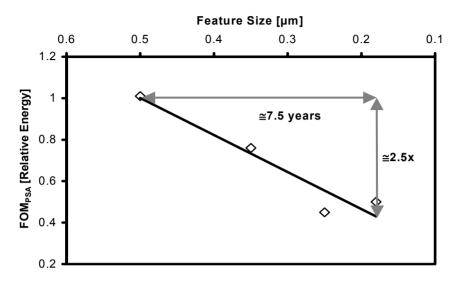

In order to relate this data to progress over time, we now construct a speed/scaling trajectory. For the four marked data points in Figure 3-11, we assume a typical average flash ADC speed of 350MHz in  $0.5\mu$ m technology, and a throughput doubling every two process generations (see chapter 2). This choice is somewhat arbitrary, but fairly reasonable. The resulting power efficiency versus feature size is plotted in Figure 3-12.

*Figure 3-11.* Flash ADC energy as a function of sampling rate (assuming improving mismatch factors  $A_{VT}$ , and  $A_{\beta}$  with technology).

*Figure 3-12.* Estimated flash ADC energy versus feature size (from speed trajectory in Figure 3-11).

## 4.4 Flash ADC Performance Trends

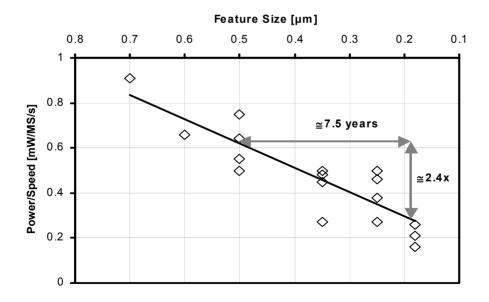

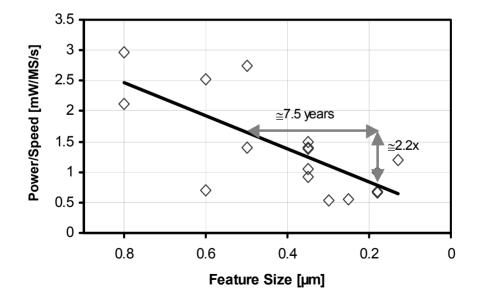

It is interesting to compare the result above to published performance data. The data summarized in Table 3-1 is plotted in Figure 3-13 against feature size. Here, we compare only flash ADCs with a fixed resolution of 6 bits, and hence use *FOM3* as defined in equation (2-5). The linear fits to the data points of Figure 3-12 and Figure 3-13 show a remarkably close energy efficiency improvement rate of roughly 2.5x over the 7.5 years spanned by the four technology nodes under investigation. This corresponds to a 2x energy reduction every 5.7 years.

Note that this progress rate is significantly worse than that seen in the global energy per conversion survey of chapter 2 (*FOM*2 improves 2x every 2.7 years). This observation indicates that energy efficiency of flash ADCs may not scale as well as that of other ADC topologies.

| Reference | Feature<br>Size [µm] | Year | Speed<br>[MS/s] | Power<br>[mW] | Supply<br>[V] | FOM3=Power/Speed<br>[mW/MS/s] |

|-----------|----------------------|------|-----------------|---------------|---------------|-------------------------------|

| [45]      | 0.70                 | 1996 | 175             | 160           | 3.3           | 0.91                          |

| [46]      | 0.60                 | 1999 | 500             | 330           | 3.0           | 0.66                          |

| [47]      | 0.50                 | 1996 | 200             | 110           | 3.0           | 0.55                          |

| [48]      | 0.5                  | 1998 | 350             | 225           | 5             | 0.64                          |

| [49]      | 0.5                  | 1998 | 400             | 200           | 5             | 0.5                           |

| [50]      | 0.5                  | 1998 | 200             | 150           | 5             | 0.75                          |

| [51]      | 0.35                 | 1998 | 400             | 190           | 3.0           | 0.48                          |

| [52]      | 0.35                 | 1999 | 500             | 225           | 3.3           | 0.45                          |

| [53]      | 0.35                 | 2001 | 1100            | 300           | 3.3           | 0.27                          |

| [54]      | 0.35                 | 2001 | 1000            | 500           | 3.3           | 0.5                           |

| [55]      | 0.25                 | 2003 | 1300            | 600           | 1.8           | 0.46                          |

| [56]      | 0.25                 | 2002 | 400             | 150           | 2.2           | 0.38                          |

| [57]      | 0.25                 | 2000 | 700             | 187           | 3.3           | 0.27                          |

| [58]      | 0.25                 | 2000 | 800             | 400           | 3.3           | 0.50                          |

| [59]      | 0.25                 | 2001 | 900             | 450           | 2.5           | 0.50                          |

| [60]      | 0.18                 | 2003 | 2000            | 310           | 1.8           | 0.16                          |

| [61]      | 0.18                 | 2003 | 400             | 106           | 1.8           | 0.26                          |

| [62]      | 0.18                 | 2002 | 1600            | 340           | 1.9           | 0.21                          |

Table 3-1. 6-bit Flash ADC Performance.

Figure 3-13. Published flash ADC performance vs. technology.

### 4.5 Discussion

The energy efficiency of flash ADCs in scaled technologies depends strongly on the scaling behavior of matching performance. If matching did not scale, moving to smaller feature sizes would be justified only by a need for a higher speed that is not feasible in a previous technology. Since matching generally improves with technology, we have seen not only higher throughput in flash ADCs, but also improved power efficiency.

Despite the good agreement in the above data, we must be aware of several limitations in the accuracy of this prediction: First, we neglected the digital portion of the ADC. In some designs, the digital circuitry of a flash converter consumes 40-60% of the total power [45, 47]. With the data for energy efficiency of digital circuits from chapter 2 (2x improvement every 1.7 years), this suggests that we should actually see a faster net rate of progress than that seen in Figure 3-12.

Secondly, both our analysis and survey do not take any second order dynamic performance limitations into account. Achieving significantly higher speed in new technologies places stringent requirements on timing and circuit topology, which may adversely affect the complexity and power consumption of the design.

Lastly, the analysis does not conclude topological advancements, such as the use of offset cancellation techniques or interpolation. Increasing design expertise is an important factor in progress, but it is virtually impossible to capture.

Nevertheless, the results above provide good qualitative insight into the scaling behavior of matching-limited circuits and help explain the trends of the past decade.

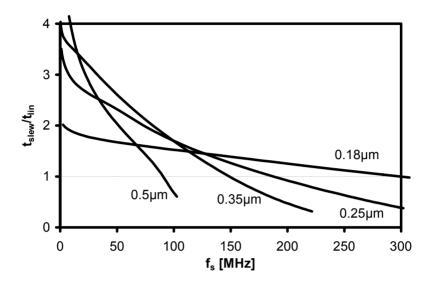

# 5. SCALING IMPACT ON NOISE-LIMITED CIRCUITS

In high-resolution ADCs, the power consumption tends to be set by noise constraints rather than matching. In cases where matching is critical, the desired accuracy is usually achieved through some form of calibration. As an example for a noise-limited circuit, we examine a basic transconductor in feedback configuration. To first order, this circuit resembles the precision amplifiers used in the front-end of sigma-delta and pipelined ADCs.

#### 5.1 First Order Analysis

A very basic analysis for noise-limited transconductors was presented in [30]. For a noise limited circuit, an appropriate figure of merit is given by

$$FOM_{PSD} = \frac{Power}{Speed \cdot DynamicRange}$$

. (3-20)

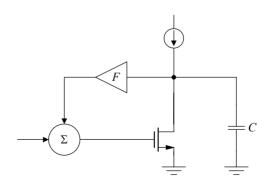

Consider now the circuit of Figure 3-14 to identify the individual variables of (3-20).

In this circuit, we assume a single transistor amplifier in a "constant" feedback network, i.e. we assume that device loading does not alter the feedback factor F. Furthermore, we assume that the available output swing is proportional to the technology's  $V_{DD}$  and the total integrated noise in the circuit is set by the load capacitor C. If we also assume that the transconductor efficiency  $g_m/I_D$  is kept constant with technology scaling, we obtain

$$FOM_{PSD} \propto \frac{V_{DD} \cdot I_D}{\frac{g_m}{C} \cdot \frac{V_{DD}^2}{kT/C}} \propto \frac{1}{V_{DD}}$$

(3-21)

This result states that noise-limited analog power consumption will scale inversely with the technology's supply voltage  $V_{DD}$ . For instance, scaling from 0.5µm with  $V_{DD}$ =5V to 0.25µm with  $V_{DD}$ =2.5V would double power consumption.

Figure 3-14. Basic amplifier model.

From the trends seen in the previous chapter, it is clear this result overestimates the scaling penalty. In the following sections we will investigate several second order factors that help improve the accuracy of our prediction.

# 5.2 Modified Analysis

The simple circuit model of Figure 3-14 fails to capture a number of effects that may be significant when trying to predict scaling behavior. In the following sections, we list and examine additional considerations.

#### 5.2.1 Feedback Factor F

As technology scales, capacitive loading of the (capacitive) feedback network by the device  $C_{gs}$  decreases. Since circuit speed is proportional to F, improvements in F can translate into lower power at a given speed, and thus help to counteract power increase with scaling. However, in high dynamic range circuits it is usually true that  $C_{gs} << C_{feedback}$ . We therefore consider this effect as insignificant within the scope of this analysis.

#### 5.2.2 Fractional Swing

The peak output swing of the transconductor is more precisely given by

$$Swing \cong V_{DD} - c \cdot V_{OV}, \qquad (3-22)$$