# **Digital Design Fundamentals**

## Second Edition

## Kenneth J. Breeding

The Ohio State University

## Prentice Hall, 1992

| eface                                              | xi                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction to Digital Systems                    | 1                                                                                                                                                                                                                                                                                                    |

| Number Systems                                     | 7                                                                                                                                                                                                                                                                                                    |

| Boolean and Switching Algebra                      | 41                                                                                                                                                                                                                                                                                                   |

| Gates and the Design of Switching Circuits         | 95                                                                                                                                                                                                                                                                                                   |

| Sequential Circuits                                | 137                                                                                                                                                                                                                                                                                                  |

| Asynchronous Sequential Circuits                   | 201                                                                                                                                                                                                                                                                                                  |

| Pulse-Mode or Multiply Clocked Sequential Circuits | 265                                                                                                                                                                                                                                                                                                  |

| Special Topics in Switching Theory                 | 301                                                                                                                                                                                                                                                                                                  |

| Large-Scale System Design                          | 353                                                                                                                                                                                                                                                                                                  |

| An Introduction to IEEE Std. 91-1984               | 419                                                                                                                                                                                                                                                                                                  |

|                                                    | Introduction to Digital Systems  Number Systems  Boolean and Switching Algebra  Gates and the Design of Switching Circuits  Sequential Circuits  Asynchronous Sequential Circuits  Pulse-Mode or Multiply Clocked Sequential Circuits  Special Topics in Switching Theory  Large-Scale System Design |

# Introduction to Digital Systems

#### □ 1.1

### WHAT IS A DIGITAL SYSTEM?

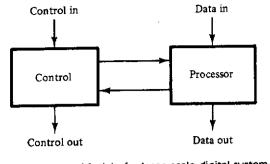

Simply put, a digital system is a system that processes discrete information. The discrete entities making up this information may represent anything from simple arithmetic integers, letters of the alphabet, or other abstract symbols to values for a voltage, a pressure, or any other physical quantity. To a digital system, what these entities represent is not important in the processing of the information. What they represent is important, however, to the human observer who must interpret the results of the process. A digital system, then, is one that accepts as input digital information representing numbers, symbols, or physical quantities, processes this input information in some specific manner, and produces a digital output.

In a large number of computer applications, the computer is required to process information related to physical quantities, such as pressure or temperature. Since nature is not digital, however, (unless, of course, one wants to go to the quantum-mechanical level), the physical quantity of time or temperature or whatever must, somehow, be converted to a digital form before it can be processed by the computer. The usual way of doing this is to first take the physical quantity to be processed and convert it into a voltage

| transducer<br>analog               | or a current. <sup>1</sup> This is done by using a transducer—a device that converts energy coming into it in one form to energy in another form at its output. A thermocouple is a good example of a temperature transducer: it produces an output voltage proportional to its ambient temperature. This output voltage becomes an analog of the temperature of the device.  We use analogs of physical quantities all the time. For example, the position of the mercury in a thermometer is an analog of the temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

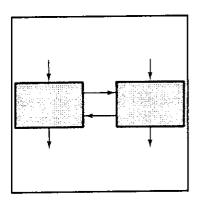

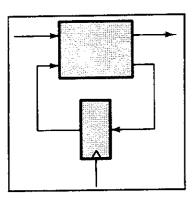

| analog-to-<br>digital<br>converter | position of the mercury in a thermometer is an analog of the temperature, and the angular position of the hands of a clock is the analog of the time. The analog of a physical quantity is, like the quantity itself, usually a continuous variable. Since a computer operates only on discrete entities, which usually can be associated with numbers, the continuous variable representing the physical quantity must first be converted to a digital form. This conversion is carried out by an analog-to-digital converter (ADC). <sup>2</sup> The digital output from the ADC, then, is a discrete approximation to the actual value of the continuous physical variable. The computer or other digital system can now process the information for whatever purpose is required.  Let us take a look at a typical digital system where these ideas are put together to perform a simple task. Suppose we have to maintain a given constant temperature in a liquid, such as the developer used in a photographic processing lab. To do this we must measure the temperature of the developer and then use the result of our measurement to turn on or turn off a heating element that surrounds the developer. To perform this task, a thermocouple might be used as the transducer that converts the temperature of the liquid to an analog voltage. This voltage would then be converted to a digital value of sufficient precision to ensure the accurate control of the temperature. The resulting digital value would then be used by some digital system, such as a microprocessor, to determine whether the heating element should be on or off. This digital system is also an example of a feedback control system, in which the result of an action taken by the system, in this case turning the heater element on or off, is "fed back" in order to determine whether a new and different action should be taken. |

|                                    | <sup>1</sup> At least, this is what might be expected of an electrical engineer. A mechanical engineer, on the other hand, might prefer to convert the physical quantity into a position of a lever or a gear. <sup>2</sup> A device that carries out the reverse process, converting a digital quantity back to an analog value, is called a digital-to-analog converter (DAC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Chapter ! Introduction to Digital Systems

### WHY ARE DIGITAL SYSTEMS SO PERVASIVE?

We might logically ask in the example above why we should use a digital system for this simple control function. After all, mechanical thermostats, which perform the given task, are readily available and inexpensive. To answer this question we need to look closer at why more and more of the everyday products that we encounter are becoming digital. There are three fundamental reasons that this is happening:

- 1. Flexibility

- 2. Reliability

- 3. Cost

Consider, for example, the temperature control system described above. It is obvious that the system described could easily be replaced by a mechanical thermostat. However, suppose we wish, at a later time, to add some features to the system, such as, for example, the ability to automatically change the temperature of the developer at different stages of the development process. Such a programmable thermostat is easily achieved using digital systems. In fact, if we were to use a microprocessor as part of such a temperature control system, we could control not only the temperature of the developer but the entire film development process. This idea is precisely why "same day" film processing services are so readily available. Clearly, it would be difficult to obtain this degree of flexibility in any other way with the ease with which we can accomplish it using a digital system.

To get some idea of how reliable digital systems can be, we need only look at the way in which information is represented in these systems. A digital system processes information in a discrete form which is normally binary. The two values of a binary digit, or bit, are 1 and 0. These values are commonly represented in a digital system by two different voltages. In fact, the 1 is usually represented by a range of voltages and the 0 by another, nonoverlapping range of voltages. In one implementing technology, the TTL (transistor-transistor logic) technology, a 1 is represented by voltages in the range of 2 to 5 volts (V) and a 0 is represented by voltages in the range of 0 to 1 V. Because these values are represented by a range of voltage, any minor change in voltage level due to noise or other external events will not cause a 0 to be misinterpreted as a 1, or vice versa. As we shall see in the next chapter, arbitrary numbers and symbols can be represented by strings of 1s and 0s. It is possible to design these digital representations so that even if noise is so large as to change the voltage corresponding to a 1 to the range for

Chapter 1 Introduction to Digital Systems

a 0, for example, the original representation can be re-created. A good exam-

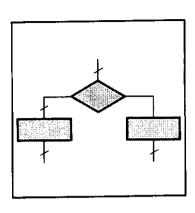

depends on the outcome of this operation.

first microprocessors, the Intel 8080. This device, which appeared in production around 1972, originally cost about \$300. Its price at one point in recent years dropped to around \$2 or less. The cost of computer memory has followed similar trends. In the 1950s, memory costs were generally figured in the dollars per bit range, whereas today the cost is more likely to be in millicents per bit. These dramatic cost reductions have come about because of advances in integrated circuit technology, specifically, the ability to put hundreds of thousands of transistors on a piece of silicon roughly 6 mm

(1 inch) on a side. Clearly, the trend is for increasingly complex functions to

ple of this is a compact disk (CD), in which digital information, representing sound, is encoded in such a way that a 1-mm hole could be drilled through the disk without the loss of a single note! Obviously, this degree of reliability makes digital systems extremely attractive for any application requiring highly reliable operation, and especially for applications where a human life

Digital systems from their very inception have been flexible and reliable. Their more recent use in every day items, such as watches, calculators, and household appliances, has come about because of their very low cost. The cost of digital devices has dropped dramatically over the past 30 years. This is illustrated by the cost of some of the 7400 series small-scale digital integrated circuits, which in the early 1960s was around \$70 apiece. These devices, which are still available and extensively used, can be purchased for less than 15 cents today. A similar reduction in cost can be seen in one of the

## □ 1.3

### **ORGANIZATION OF THE BOOK**

The purpose of this book, then, is to introduce the student to the basic concepts required to design a digital system. For this purpose the book is organized into nine chapters, each dealing with a subject either essential or just very helpful to the design of digital systems. A number of examples are given throughout the text in order to illustrate the various concepts. Each

be integrated in silicon at increasingly reduced prices.

chapter ends with an annotated bibliography giving sources for further information on topics discussed within the chapter and a set of exercise problems

<sup>&</sup>lt;sup>3</sup> An excellent discussion of this error-correction ability can be found in the article "The Digital Reproduction of Sound," by John Monforte, which appeared in the December 1984 issue of Scientific American.

which further illustrate these principles. Chapters 2 through 5 cover the essential material required for the design of any digital system, whether it be a computer or a simple controller, such as the temperature controller described in this chapter. Chapters 6 and 7 describe concepts which can make large-scale systems easier to design and more efficient in implementation. Chapter 8 discusses a number of special issues that are becoming, for one reason or another, such as VLSI (very large-scale integration) design and artificial intelligence, of increasing interest. Finally, Chapter 9, which does not heavily depend on the material in Chapters 6, 7, and 8, describes in some detail how these ideas can be put together to construct a large-scale digital system—for example, in the design of a computer or a controller for an industrial process. A very brief description of the subjects covered in each of these chapters follows.

Chapter 2 discusses number representations and methods of information coding. This chapter also discusses binary arithmetic in some detail.

Chapter 3 defines and details the algebra required for digital system design—Boolean algebra and its subset switching algebra.

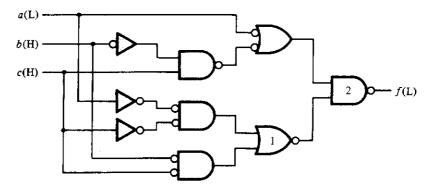

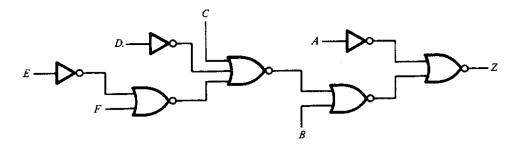

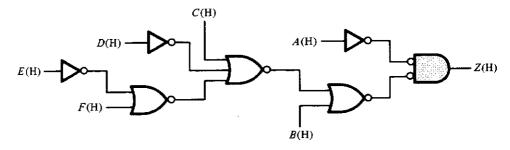

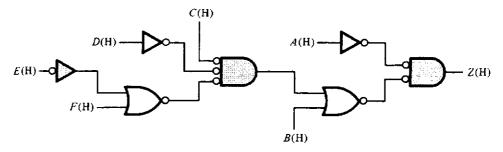

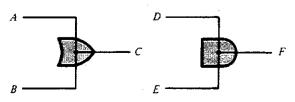

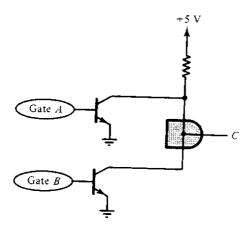

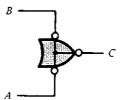

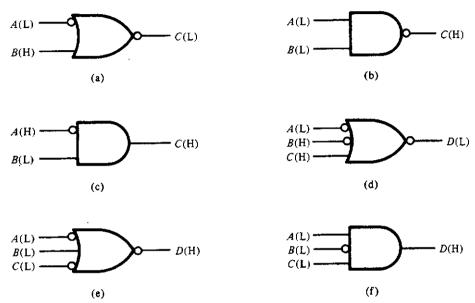

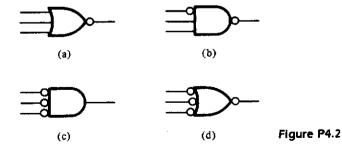

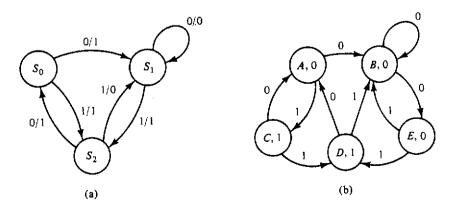

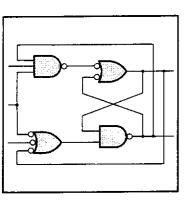

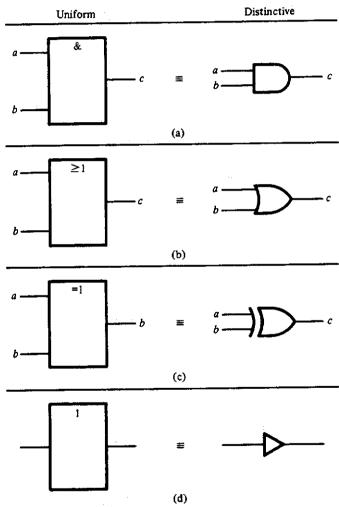

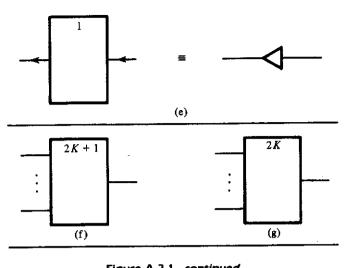

Chapter 4 introduces the fundamental building block of digital system design, the logic gate. A symbology standard that helps to clarify the operation of circuits designed using these gates is also discussed. Together with the switching algebra presented in Chapter 3, this chapter serves as an introduction to combinational circuit design. Combinational circuits are those in which the output is a function only of the circuit inputs at any given instant of time.

tim

sequential circuits

circuits

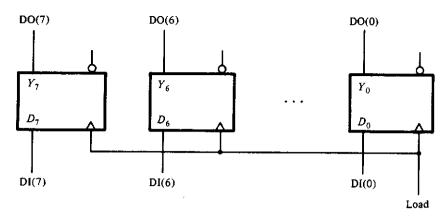

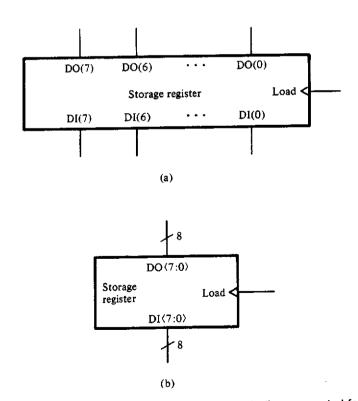

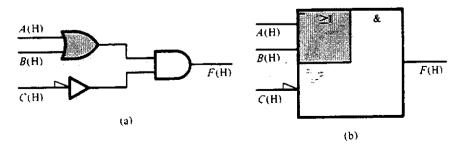

combinational

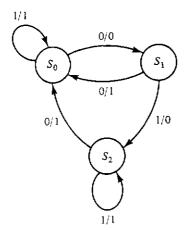

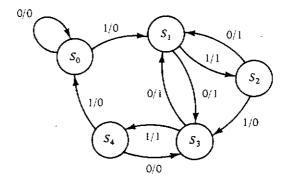

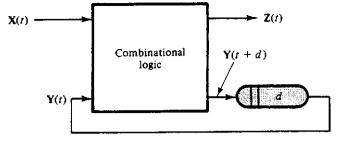

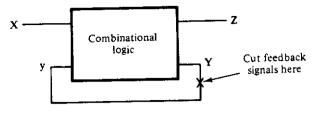

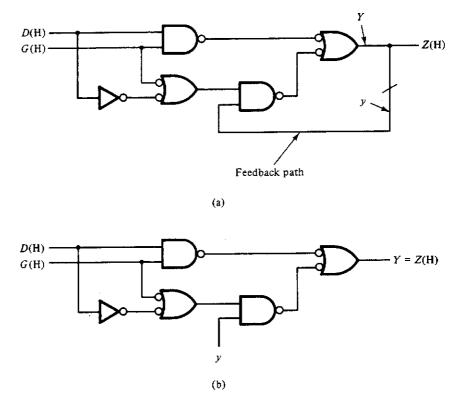

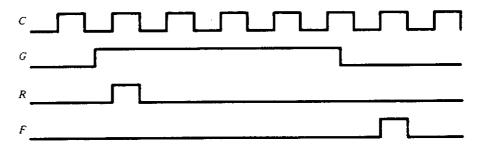

Chapter 5 introduces a class of circuits called sequential circuits, in which circuit outputs are fed back to the input. This causes the output to become a function of not only the current input but also some past sequence of inputs. This chapter also introduces the flip-flop circuit element and shows how this device can be used in the sequential circuit to control the time at which the outputs change. Since this time of change is controlled by a single system clock, circuits of this type are generally referred to as synchronous or clocked sequential circuits. This is the class of sequential circuits that is generally used to control the operations within a computer.

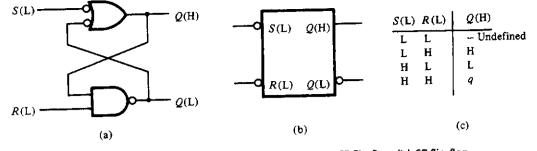

In Chapter 6, sequential circuits that are not controlled by a clock are investigated. Since no clock is present in such a system to synchronize the circuit outputs, such circuits are referred to as asynchronous sequential circuits, or sequential circuits operating in the fundamental mode. Flip-flops themselves are analyzed and designed in this chapter, along with many other very useful fundamental-mode devices.

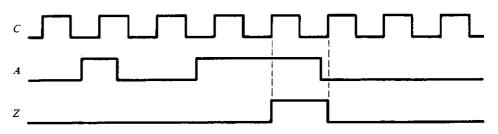

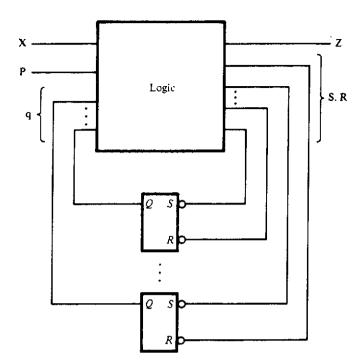

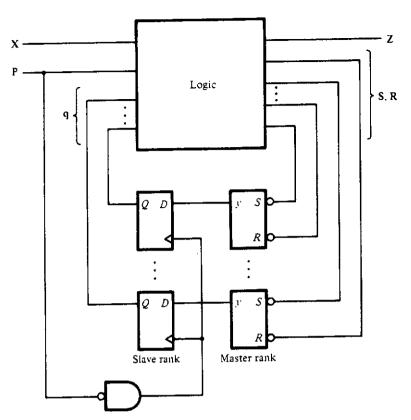

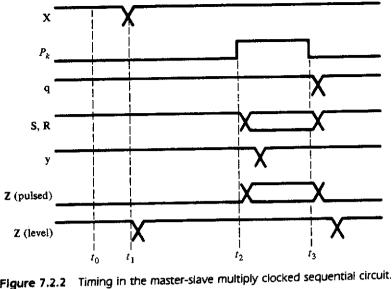

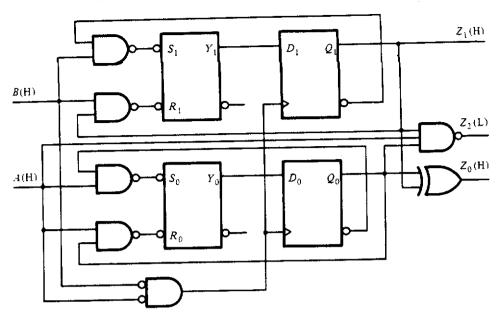

Chapter 7 deals with sequential circuits in which more than one clock signal is present. We will refer to such systems as multiply clocked sequential circuits. This chapter also briefly discusses a particular subclass called

6 Chapter 1 Introduction to Digital Systems

pulse-mode circuits, in which the input clock signals are considered to be very short pulses.

In Chapter 8 a number of special topics are introduced that are important topics are special topics are introduced that are important topics are introduced topics are introduced topics.

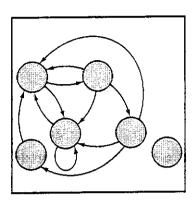

In Chapter 8 a number of special topics are introduced that are important in various application areas of digital systems; for example, VLSI design and artificial intelligence.

Finally, Chapter 9 applies the ideas developed in preceding chapters to the design of large-scale digital systems. This chapter gives a model for such systems and presents methods for organizing their design.

# **Digital Design Fundamentals**

## Second Edition

## Kenneth J. Breeding

The Ohio State University

## Prentice Hall, 1992

| eface                                              | xi                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction to Digital Systems                    | 1                                                                                                                                                                                                                                                                                              |

| Number Systems                                     | 7                                                                                                                                                                                                                                                                                              |

| Boolean and Switching Algebra                      | 41                                                                                                                                                                                                                                                                                             |

| Gates and the Design of Switching Circuits         | 95                                                                                                                                                                                                                                                                                             |

| Sequential Circuits                                | 137                                                                                                                                                                                                                                                                                            |

| Asynchronous Sequential Circuits                   | 201                                                                                                                                                                                                                                                                                            |

| Pulse-Mode or Multiply Clocked Sequential Circuits | 265                                                                                                                                                                                                                                                                                            |

| Special Topics in Switching Theory                 | 301                                                                                                                                                                                                                                                                                            |

| Large-Scale System Design                          | 353                                                                                                                                                                                                                                                                                            |

| An Introduction to IEEE Std. 91-1984               | 419                                                                                                                                                                                                                                                                                            |

|                                                    | Introduction to Digital Systems  Number Systems  Boolean and Switching Algebra Gates and the Design of Switching Circuits Sequential Circuits Asynchronous Sequential Circuits Pulse-Mode or Multiply Clocked Sequential Circuits Special Topics in Switching Theory Large-Scale System Design |

| Decimal | BCD  | Excess 3 |

|---------|------|----------|

| 0       | 0000 | 0011     |

| L       | 0001 | 0100     |

| 2       | 0010 | 0101     |

| 3       | 0011 | 0110     |

| 4       | 0100 | 0111     |

| 5       | 0101 | 1000     |

| 6       | 0110 | 1001     |

| 7       | 0111 | 1010     |

| 8       | 1000 | 1011     |

| 9       | 1001 | 1100     |

|         |      |          |

# **Number Systems**

#### 🗌 2.1

#### INTRODUCTION

It may be obvious that a digital computer operates only on numbers. The way in which the machine operates on these numbers, however, is a function of what the numbers represent (do they represent themselves, other numbers, or alphanumeric characters?) and in what form they are represented. Clearly, the design of the central processing unit, the portion of the computer that handles all arithmetic and logic operations, cannot be carried out without a complete knowledge of the form in which the numbers are represented in the machine. Furthermore, this form is generally quite different from the way numbers must be represented to the human operator, and so there has to be some type of conversion in the computer input/output system.

The purpose of this chapter, then, is to discuss the various ways in which numbers and other quantities are represented and manipulated in a computer. In addition, various forms of data encoding, as well as binary arithmetic, will be examined.

### □ 2.2

### BASE CONVERSION

The number system we most often use is the decimal system. For various reasons, which will be examined later, the decimal number system is not a convenient one for a computer to use. Computers work most efficiently on information that is binary. Since computers are not good with decimal numbers and people are generally not very proficient with the use of binary numbers, some type of conversion between these systems must occur at the interface between people and computers. In this section we examine the various issues involved in the conversion.

#### Radix r-to-Decimal Conversion 2.2.1

A positional notation has long been used for writing numbers. In such a representation the position of each digit indicates the weight associated with the digit. In particular, the number 276.5 would be interpreted as

The various powers of 10 used in this representation, which are the respec-

$$2 \times 10^2 + 7 \times 10^1 + 6 \times 10^0 + 5 \times 10^{-1} = 276.5$$

(2.2.1)

tive weights, are indicative of the assumption that the number 276.5 was written as a decimal number, or a number written in base 10. The base of a

number is also referred to as the radix of the system.

In general, the radix of a system can be anything; 5 or 12 or -3, or even an irrational number, such as  $\pi$  or e. Usually, however, the radix of number systems is taken as a positive integer. When a number is written in a base other than 10, the radix used must somehow be noted so that the number can be properly interpreted. Usually, this is indicated by placing the number in parentheses and attaching a subscript at the end to indicate the base. Thus (1321)<sub>4</sub> indicates that the number 1321 has a radix of 4 and would be interpreted as follows:

$$(1321)_4 = 1 \times 4^3 + 3 \times 4^2 + 2 \times 4^1 + 1 \times 4^0 \tag{2.2.2}$$

Note that if the arithmetic in Equation (2.2.2) is carried out in the decimal system, the number (1321)<sub>4</sub> must be the same as the number 121 in base 10!

In general, a number of radix r,  $A_r$ , can be written as

radix

<sup>1</sup> The Roman numeral system is an example of a system that uses a nonweighted notation for representing numbers.

$$A_r = (a_n a_{n-1} \cdot \cdot \cdot a_0 \cdot a_{-1} \cdot \cdot \cdot a_{-m})_r = \sum_{i=-m}^n a_i r^i$$

(2.2.3)

radix point

where the  $a_i$  are digits in the radix r system and where the point (.) is termed the radix point, which, as is customary, separates the integral and fractional parts of the number. Carrying out the arithmetic of Equation (2.2.3) in the decimal number system results in the decimal equivalent of  $A_r$ . For example, consider the problem of finding the decimal number equivalent to (364.213)<sub>7</sub>. The value is found by using the notation of Equation (2.2.3) as follows:

$$(364.213)_7 = 3 \times 7^2 + 6 \times 7^1 + 4 \times 7^0 + 2 \times 7^{-1} + 1 \times 7^{-2} + 3 \times 7^{-3}$$

=  $(193.314868 . . .)_{10}$

where the trailing points indicate that additional fractional digits occur.

#### 2.2.2 Decimal-to-Radix r Conversions

Conversion from some radix r to decimal is quite straightforward, as just indicated. The question that naturally arises next is how to convert from decimal to an arbitrary radix equivalent. To see how this process may be carried out, let  $B_{10}$  be a given decimal number that is to be converted to a number  $A_r$  radix r. That is,

$$B_{10} = A_r = (a_n a_{n-1} \cdot \cdot \cdot a_0)_r$$

(2.2.4)

or, expanding  $A_r$ ,

$$B_{10} = a_n r^n + a_{n-1} r^{n-1} + \cdots + a_1 r^1 + a_0$$

(2.2.5)

Now, if  $B_{10}$  is divided by r, Equation (2.2.5) becomes

$$\frac{B_{10}}{r} = (a_n r^{n-1} + \dots + a_2 r + a_1) + \frac{a_0}{r}

= \operatorname{Int}\left(\frac{B_{10}}{r}\right) + \operatorname{Frac}\left(\frac{B_{10}}{r}\right)$$

(2.2.6)

where Int and Frac indicate the integral and fractional parts of  $B_{10}/r$ . From Equation (2.2.6), we see that

$$a_0 = \operatorname{Rem}\left(\frac{B_{10}}{r}\right) \tag{2.2.7}$$

where Rem means the remainder of  $B_{10}/r$ . If this process is now repeated starting with  $Int(B_{10}/r)$ , the next remainder will be  $a_1$  and the next integral part will be  $a_n r^{n-2} + a_{n-1} r^{n-3} + \cdots + a_2$ . Continuing this process until no integral part remains will produce the digits of  $A_r$ .

Consider as an example the problem of finding the base 3 equivalent of  $(278)_{10}$ . The work may be carried out as follows:

| Quotient      | Remainder |

|---------------|-----------|

| 3 <u>)278</u> |           |

| 3 <u>)92</u>  | $2 = a_0$ |

| 3 <u>)30</u>  | $2=a_1$   |

| 3 <u>)10</u>  | $0=a_2$   |

| 3 <u>)3</u>   | $1 = a_3$ |

| 3 <u>)1</u>   | $0=a_4$   |

| 0             | $1=a_5$   |

| Stop          |           |

Thus

$$(278)_{10} = (101022)_3$$

As a check, convert (101022)<sub>3</sub> back to decimal:

$$(101022)_3 = 1 \times 3^5 + 1 \times 3^3 + 2 \times 3 + 2 = (278)_{10}$$

Numbers, in general, have fractional parts as well as integral parts. Conversion of these fractional parts to an equivalent radix r representation may be carried out in a manner similar to the conversion of the integral parts. Let  $B_{10}$  now represent a fractional decimal number equivalent to a fractional number  $A_r$  in radix r. Thus

$$B_{10} = A_r = (0.a_{-1}a_{-2} \cdot \cdot \cdot a_{-m})_r$$

=  $a_{-1}r^{-1} + a_{-2}r^{-2} + \cdot \cdot \cdot + a_{-m}r^{-m}$  (2.2.8)

Multiplying the result of Equation (2.2.8) by r yields

$$rB_{10} = a_{-1} + (a_{-2}r^{-1} + \cdots + a_{-m}r^{-m+1})$$

(2.2.9)

from which the integral part becomes  $a_{-1}$ . The fractional part,  $(a_{-2}r^{-1} + \cdots + a_{-m}r^{-m+1})$ , when multiplied by r yields  $a_{-2}$ , and so on. Thus repeated multiplication by r yields the successive digits of the radix r representation of the fractional number  $B_{10}$ .

As an example, consider the conversion of  $(0.27)_{10} = (?)_4$ . The process goes as follows:

| Integer      | Fraction   |

|--------------|------------|

|              | .27        |

|              | <u>×4</u>  |

| $a_{-1} = 1$ | .08        |

|              | $\times 4$ |

| $a_{-2} = 0$ | .32        |

|              | $\times 4$ |

| $a_{-3} = 1$ | .28        |

|              | $\times 4$ |

| $a_{-4} = 1$ | .12        |

|              | •          |

|              | •          |

|              | -          |

Thus  $(0.27)_{10} = (0.1011 . . .)_4$ , and as a check,

$$(0.1011 ...)_4 = 1 \times 4^{-1} + 1 \times 4^{-3} + 1 \times 4^{-4} + \cdots$$

=  $(0.2695 ...)_{10}$

As is generally the case, this conversion process yields a nonexact equivalent. This fact must be taken into account when computation is done with a computer not using the decimal system.

The conversion of general decimal numbers with both integral and fractional parts can now easily be handled by simply converting each part separately and combining the results. For example, solve the equation  $(123.56)_{10} = (?)_7$ . First, convert the integral part:

Next, convert the fractional part:

3 .92 ×7 6 .44 ×7 3 .08 ×7 0 .56

The result then becomes

$$(123.56)_{10} = (234.3630 . . .)_7$$

where, as usual, the trailing points mean the result is not exact.

Conversion between two nondecimal systems can be handled most easily by using the decimal system as an intermediate step. For example, the problem of solving  $(1354.24)_6 = (?)_4$  would be accomplished by first converting from base 6 to base 10 and then converting this base 10 number to base 4. Thus

$$(1354.24)_6 = (358.4444 . . .)_{10}$$

=  $(11212.1301 . . .)_4$

## 2.2.3 Counting in a Radix r System

In the conversion process just described, it is interesting to note that the only numerical values the digits may take fall in the range of 0 to r-1. Furthermore, note that

$$10_r = 1 \times r^1 + 0 \times r^0 = r_{10} \tag{2.2.10}$$

Because of these two observations, counting in radix r always produces the sequence of numbers 0, 1, 2, ..., (r-1), 10, 11, 12, ..., 1(r-1), ... Figure 2.2.1 shows the counting sequence for various radices.

| Decimal | r = 2 | r = 3 | r = 8 |                                |

|---------|-------|-------|-------|--------------------------------|

| 0       | 0     | 0     | 0     | -                              |

| 1       | 1     | 1     | 1     |                                |

| 2       | 10    | 2     | 2     |                                |

| 3       | 11    | 10    | 3     |                                |

| 4       | 100   | 11    | 4     |                                |

| 5       | 101   | 12    | 5     |                                |

| 6       | 110   | 20    | 6     |                                |

| 7       | 111   | 21    | 7     |                                |

| 8       | 1000  | 22    | 10    |                                |

| 9       | 1001  | 100   | 11    |                                |

| 10      | 1010  | 101   | 12    | Figure 2.2.1                   |

| 11      | 1011  | 102   | 13    | Counting in various systems of |

| 12      | J100  | 110   | 14    | different radix r.             |

When r > 10, a problem arises in the representation of those digits x in the range 9 < x < r, since no standard symbols exist for these numbers. By convention, capital letters are used to represent these digits. Thus, for r = 16 (the hexadecimal system), the counting sequence would be  $0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F, 10, ..., where <math>(A)_{16} = (10)_{10}$ ,  $(B)_{16} = (11)_{10}$ , and so on.

## 2.2.4 Binary, Octal, and Hexadecimal Conversions

Normally, computations within a computer are carried out in the binary, or base 2, system. This is principally because digital circuits are usually two-state devices. Circuit elements having more than two states do exist, but these generally suffer from low reliability and other difficulties, some of which will be alluded to later.

Conversion from binary to decimal, and vice versa, is carried out as described above but is generally much easier than conversions between decimal and a radix larger than 2. An example will help illustrate: Convert  $(132)_{10}$  to  $(x)_2$ . The conversion goes as follows:

| 2 <u>)132</u> |   |

|---------------|---|

| 2 <u>)66</u>  | 0 |

| 2 <u>)33</u>  | 0 |

| 2 <u>)16</u>  | 1 |

| 2 <u>)8</u>   | 0 |

decimal to binary and thus  $(132)_{10} = (10000100)_2$ , which, as a check, yields

$$2^7 + 2^2 = 128 + 4 = (132)_{10}$$

In a binary number, each binary digit, or bit, is weighted as a power of 2. Thus, as this example illustrates, conversion from binary to decimal requires only the addition of the powers of 2 corresponding to the 1s in the number.

Generally, working with binary numbers is somewhat cumbersome, because of the large number of bits required to make up even small decimal equivalents. For this reason, the *octal* and *hexadecimal*, or just *hex*, systems are commonly used to represent these numbers. To see the relationship between binary, octal, and hex, consider the binary number 110101011:<sup>2</sup>

$$110101011 = 1 \times 2^{8} + 1 \times 2^{7} + 0 \times 2^{6} + 1 \times 2^{5} + 0 \times 2^{4} + 1 \times 2^{3} + 0 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}$$

$$= (1 \times 2^{2} + 1 \times 2^{1} + 0 \times 2^{0})2^{6} + (1 \times 2^{2} + 0 \times 2^{1} + 1 \times 2^{0})2^{3} + (0 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0})2^{0}$$

$$= 6 \times (2^{3})^{2} + 5 \times (2^{3})^{1} + 3 \times (2^{3})^{0}$$

$$= 6 \times 8^{2} + 5 \times 8^{1} + 3 \times 8^{0}$$

$$= (653)_{8}$$

This example illustrates the extreme ease of conversion from binary to octal. The conversion simply involves grouping the bits in threes and writing the decimal value of each group. Thus

$$\frac{(101 \ 111 \ 100)_2}{= (5 \ 7 \ 4)_8}$$

In an exactly analogous fashion, the conversion from binary to hex can be simply carried out by grouping the bits in fours. Consider, for example, the following conversion:

$$(0001 \ 0111 \ 1100)_2$$

=  $(1 \ 7 \ C)_{16}$

octal hexadecimal

<sup>&</sup>lt;sup>2</sup> The subscript 2 is omitted here because the number was described as a binary number.

where C represents the twelfth hex digit.

If it is necessary to convert a number from hex to octal, or vice versa, it is generally easier to use binary rather than decimal as the intermediate step. For example,

$$(1A8E)_{16} = (?)_8 = (0001 \ 1010 \ 1000 \ 1110)_2$$

=  $(001 \ 101 \ 010 \ 001 \ 110)_2$

=  $(1 \ 5 \ 2 \ 1 \ 6)_8$

The result here is obtained by doing nothing more than writing the hex number in binary and then regrouping the bits to form the octal result.

#### **□ 2.3**

#### BINARY ARITHMETIC

Carrying out arithmetic operations in binary may take a bit of getting used to, but it is generally simpler than it is in decimal, since the addition and multiplication tables are so simple. These tables are given in Figure 2.3.1.

addition

Consider as an example of the addition process the sum of the two binary numbers A = 10111010 and B = 110111. The addition is carried out as follows:

As a check, we note that  $A = (186)_{10}$  and  $B = (55)_{10}$ , and thus the decimal value of A + B is 241, which is equal to binary 11110001.

In carrying out the addition in the example above, a number of incidents occurred where more than two bits had to be added. This, of course, was caused in each case by the carry generated by the addition of the previous

$$\begin{array}{lll} 0+0=0 & 0\times 0=0 \\ 0+1=1 & 0\times 1=0 \\ 1+1=10 & 1\times 1=1 \\ (a) & (b) & \text{for binary numbers.} \end{array}$$

Figure 2.3.1

| Carry in | <b>A</b> , | Bi | Sum, | Carry out |

|----------|------------|----|------|-----------|

| 0        | 0          | 0  | 0    | 0         |

| Ö        | 0          | 1  | 1    | 0         |

| Ō        | i          | 0  | 1    | 0         |

| 0        | 1          | 1  | 0    | 1         |

| 1.       | . 0        | 0  | 1    | 0         |

| i        | 0          | 1  | 0    | 1         |

| i        | 1          | 0  | 0    | 1         |

| i        | 1          | 1  | 1 1  | 1         |

|          |            |    |      |           |

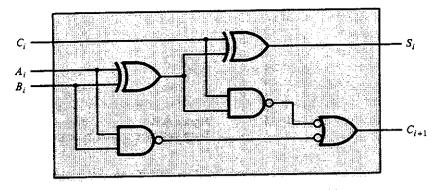

Figure 2.3.2 Addition table including carries.

bits. An alternative representation for the addition table of Figure 2.3.1 which includes the carry to be added as well as the carry generated is given in Figure 2.3.2. It will be shown later that this table can be used, in the form given, to generate hardware that performs binary addition in a computer's central processing unit. In using this table it should be noted that the number in the "carry in" column of the table is the carry that has been generated by addition of the numbers in the previous column, i-1, of bits and the carry out is the carry in of the next column of bits, i+1.

multiplication

As with decimal arithmetic, multiplication uses both the multiplication table and the addition table. The process is carried out by first multiplying the multiplicand by each digit of the multiplier to form a set of partial products. These partial products are then added to form the final product. For example,

| 101100        | multiplicand     |

|---------------|------------------|

| × <u>1011</u> | multiplier       |

| 101100        |                  |

| 101100        | partial products |

| 000000        |                  |

| 101100        |                  |

| 111100100     | product          |

This result is easily checked by multiplying the decimal equivalents of the binary multiplicand and multiplier as follows:

$$(101100)_2 \times (1011)_2 = 44 \times 11 = 484 = (111100100)_2$$

Subtraction and division introduce the same extra complexities in binary as they do in decimal arithmetic: borrowing, and estimating quotient digits. Consider first the problem of subtraction. A subtraction table may be

subtraction

$$0-0=0$$

$1-0=1$

$1-1=0$

$0-1=1$  with a borrow from the next higher bit position Figure 2.3.3 Binary subtraction table.

set up in the manner shown in Figure 2.3.3; the table is similar in form to the addition table given in Figure 2.3.1. Using this table, the difference between the two binary numbers 10000 and 101 is computed as follows:

Some other examples are as follows:

$$1010 - 1 = 1001$$

$110010 - 101 = 101101$

$1101 - 100101 = -11000$

It will be shown in the next section that subtraction can actually be performed by first "coding" the subtrahend and then using addition, thus avoiding the various complications arising because of the borrows.

Long division may be carried out in binary in a manner equivalent to decimal division, but it is generally much easier, since there is virtually no need for estimation of quotient digits. An example will best illustrate the process. Consider the problem of determining 100101/101. There are many ways of organizing the work. However, a classic approach is as follows:

$$\frac{111}{101)100101} = \text{quotient}$$

$\frac{101}{1000}$

$\frac{101}{111}$

$\frac{101}{101}$

$10 = \text{remainder}$

division

| 18 | Chapter 2 Number Systems                                                     |  |

|----|------------------------------------------------------------------------------|--|

|    | Thus 100101/101 = 111 with a remainder of 10; or, as a check, in decimal the |  |

|    | 1 mus 100101/101 111 (10) A-                                                 |  |

division problem becomes  $37/5 = 7 = (111)_2$  with a remainder of  $2 = (10)_2$ . As a second example, consider the problem 11010111/110:  $\frac{100011}{11010111}$

| 110/11010111 |

|--------------|

| <u>110</u>   |

| 1011         |

| <u> 110</u>  |

| 1011         |

| <u>_110</u>  |

| 101          |

Here the result is 100011 with a remainder of 101, or, in decimal, as a check, 215/6 = 35 with a remainder of 5.

Notice that in both examples, estimating whether or not the divisor will go into a partial dividend requires only the step of determining whether or

go into a partial dividend requires only the step of determining whether or not the partial dividend is greater than or equal to the divisor. If it is, the value that is put into the quotient has to be a 1; the divisor is then subtracted from the partial dividend. If it is not, a 0 is placed in the quotient and the next bit of the dividend is brought down; the process is repeated until a 1 can be placed in the quotient and the divisor can be subtracted from the resulting partial dividend.

## COMPLEMENT ARITHMETIC

metic operations.

It was mentioned in Section 2.3 that subtraction can be carried out by using addition if the subtrahend is "coded" properly. The implication of this, with regard to the design of a computer, is that a single piece of hardware, an adder, can be used to perform all arithmetic operations. This happens because binary multiplication involves addition only and binary division involves subtraction only. This clearly simplifies the design process as well as the designed hardware. The purpose of this section, then, is to describe this coding and show how it can be used for number representation and arith-

## 2.4.1 Radix and Diminished Radix Complements

Let A be an n-digit integer in radix r representation. Then the radix complement of A is defined as

radix complement

🗌 2.4

$$A^* = \text{radix complement of } A = r^n - A$$

(2.4.1)

diminished radix complement and the diminished radix complement is defined as

$$A^+$$

= diminished radix complement of  $A = r^n - A - 1$  (2.4.2)

To see how the complement representation of a number can be used in the subtraction process, let A and B be two n-digit numbers<sup>3</sup> and suppose that B - A is to be determined. The claim is that the difference can be found by adding the radix complement of A to B, or

$$A^* + B = r^n - A + B$$

=  $r^n + (B - A)$  (2.4.3)

Recall from the preceding section that  $r_{10} = 10_r$ . Thus  $r^n$  in radix r arithmetic is just 1 followed by n zeros. Two possible cases occur here. First, assume that B > A. Then the result is positive and Equation (2.4.3) yields the correct n-digit difference preceded by a 1. An example may help. Let A = 0592 and B = 3456 be two 4-digit decimal numbers. From Equation (2.4.1),

$$A^* = 10000 - 0592 = 9408 \tag{2.4.4}$$

and adding this complement to B, we obtain

$$B + A^* = 3456 + 9408 = 1 2864$$

Ignoring the 1, +2864 is, of course, the correct answer.

The second case occurs when A > B. In this case, Equation (2.4.3) may be written as  $r^n - (A - B)$ , and since A - B is now positive, the result is, by definition of the radix complement in Equation (2.4.1), the radix complement of A - B! That is, the result is a negative number that is in radix complement form. For example, let A = 6734 and B = 523; then, as before,

$$A^* = 10000 - 6734 = 3266 \tag{2.4.5}$$

and adding this to B, we have

$$B + A^* = 523 + 3266 = 3789$$

which is the radix complement of 6211, the difference between 6734 and 523. Here, however, the result is negative.

<sup>&</sup>lt;sup>3</sup> If the two numbers do not have the same number n of significant digits, then the smaller may have zeros appended on the left to make up the necessary n digits.

In the first case, where B-A was positive, n+1 digits appeared in the complement sum, with the leftmost being ignored and the remaining digits being the magnitude of the correct answer. In the second case, where B-A was negative, the complement sum had only n digits and was the radix complement of the answer. In this case the magnitude of the answer can be found by taking the radix complement. In both cases, however, the difference of A and B was found by the use of addition (ignoring for the moment

that the complement was found by subtraction).

This process is particularly simple when applied to binary numbers. Consider, for example, the subtraction of A = 110101 from B = 111001, that is, the problem B - A = (?). The first step is to find the 2's complement of A. In this case both numbers have 6 bits, making n = 6 in Equation (2.4.1), so

$$A^* = 1000000 - 110101$$

Before carrying out this subtraction, note that from Equation (2.4.2)

$$A^* = A^+ + 1 \tag{2.4.6}$$

so that

$$A^* = (1000000 - 1 - A) + 1$$

$$= (111111 - 110101) + 1$$

$$= (001010) + 1$$

$$= 001011$$

The important thing to observe from this is the extreme ease with which the 1's complement is found: simply interchange 1s and 0s, which requires no subtraction at all. The 2's complement is then obtained by adding 1. Continuing with the problem now requires that  $A^*$  be added to B to obtain the answer:

$$A^{*} + B = 001011 + 111001 = 1 000100$$

Since the result has a carry out of the sixth bit position, the result is positive and has a value of 100. This, of course, can be checked by simply subtracting the original two arguments.

In this example, absolutely no subtraction was used to obtain the difference between two binary numbers, since the 2's complement of A was found by interchanging 1s and 0s and then adding 1 to the result. It is important to remember that both numbers must contain the same number of bits at the start. Some further examples will illustrate this procedure.

$$1011011 - 0010110 = 1011011 + 1101001 + 1$$

= 1 1000101 (positive)

$10011 - 10111 = 10011 + 01000 + 1 = 11100$  (negative 00100)

$110100110 - 11001 = 110100110 + 111100110 + 1$

= 1 110001101 (positive)

$1 - 100000 = 000001 + 011111 + 1 = 100001$  (negative 011111)

In each of these examples the 2's complement was generated by taking the 1's complement and adding 1. A very simple, and mechanical, alternative to this is the following. Starting on the right and moving to the left, copy the rightmost zeros until reaching the first 1. Copy this 1. From this point on copy the complements of the remaining bits. For example, to convert A = 10110100 to its 2's complement form, we proceed as follows:

|       |   | Complement | Сору |

|-------|---|------------|------|

| A     | = | 10110      | 100  |

| $A^*$ | = | 01001      | 100  |

This simple procedure works because in taking the 1's complement of A, the rightmost three bits would become 011. After adding 1 to obtain the 2's complement, these bits become 100, the original right three bits.

Before proceeding to examine how the sign of a number can be made part of the number, let us go back for a moment to the decimal system. Equation (2.4.6) may be used to compute the 10's complement of  $A^*$  in Equation (2.4.4) in a particularly simple manner. Specifically,

$$A^* = (10000 - 1 - 0592) + 1$$

$$= (9999 - 0592) + 1$$

$$= 9407 + 1$$

$$= 9408$$

Notice that although subtraction was required to get the 9's complement, it was a particularly simple subtraction requiring no borrows. This occurred because each digit of A was subtracted from 9 to obtain the corresponding digit of  $A^+$ . Thus, converting A to  $A^+$  requires at each digit position only a knowledge of that digit and not the whole number. This can be done by a "table look-up" procedure (as will be described in Section 2.5.4), which requires no subtraction at all.

Subtraction can also be carried out using the diminished radix complement. In this case, however, the carries cannot be ignored. Using the dimin-

carry

end-around

and adding, we obtain the result

Chapter 2 Number Systems

111001 + 010010  $\angle 001011$

001100

(1's complement of 101101) add end-around carry As was the case for the radix complement, the generation of a carry implies

that the result of the addition is positive. The absence of a carry implies a negative result. Problem 2.11 at the end of this chapter explores the reason for the end-around carry. One problem with the diminished radix complement is that the representation for the number 0 is not unique. To see this, note that the 1's

ished radix complement, if a carry is generated it must be added to the result. This addition is referred to as an end-around carry. For example, consider

the subtraction of 101101 from 111001. Taking the 1's complement of 101101

complement of 000000 is 111111. Thus both of these numbers must represent the number 0. The nonuniqueness of the number 0 is one of the reasons that the diminished radix complement is seldom used in actual designs.

In the examples just worked, the sign of the result was inferred by whether or

## 2.4.2 Binary Signed Representations

not a carry was generated out of the high-order bit position. It would be extremely useful if the sign of the number could be carried as part of the number itself. In the decimal system that most of us have grown up with, this is handled in a sign magnitude representation in which each number is preceded by a sign, such as +149 or -3765. When the sign is missing, the number is usually considered to be positive. Such a representation can work in a computer as well. However, the representation almost always used by the computer hardware is a signed 2's complement representation. In this representation, the lettmost (or most significant) bit is taken as the sign. The sign of the number is minus if this bit is 1 and plus if it is 0. The bits following the sign are either the magnitude of the number, if the sign is plus, or the 2's complement of the magnitude of the number, if the sign is minus. This representation has many advantages, not the least of which is that a string of computations may be carried out without regard to the resulting sign at each

step. The sign of the answer will be found as the sign bit of the final result. In a signed 2's complement representation it is always assumed that the number of bits in the operands is the same. In a large number of microproces-

sign magnitude

signed 2's complement

sors this number is 8 bits, which is defined as a byte. Some examples of numbers represented in this manner are the following:

| Signed 2's complement |   | Sign-magnitude |   | Decimal |

|-----------------------|---|----------------|---|---------|

| 00111010              | = | +0111010       | = | +58     |

| 11100101              | = | -0011011       | = | -27     |

| 10000001              | = | -1111111       | = | -127    |

| 01111111              | = | +1111111       | = | +127    |

By convention, the number 10000000 is taken as -128. This makes a certain degree of sense, because -127 - 1 = -128, which, when carried out in signed 2's complement arithmetic, yields 10000001 + 111111111 = (1)10000000, where the carry out of the high-order bit position, shown in parentheses, is ignored, as before. Thus numbers represented in this form using 8 bits, or a byte, can take on values ranging from -128 to +127.

To illustrate how this representation carries the sign through a string of computations, consider a couple of examples using a 4-bit signed 2's complement form (4 bits is often referred to as a *nibble*). Let A = 0011 (+3) and B = 0100 (+4). Then

$$A + B = 0011 + 0100 = 0111$$

(+7)

$A - B = 0011 + 1100 = 1111$  (-1)

$-A + B = 1101 + 0100 = 1 0001$  (+1)

where we ignore the carry, as before; and

$$-A - B = 1101 + 1100 = 1 \quad 1001 \quad (-7)$$

where again we ignore the carry. Notice in these examples that the sign bit is treated in exactly the same way as any other bit and that the carries out of the sign bit position are ignored.

The addition of two *n*-bit numbers can result in a number whose value requires more then *n* bits to represent. Such a situation is referred to as overflow if the result is positive and underflow if the result is negative. It is important that the occurrence of overflow or underflow be detected so that decisions are not based on incorrect results. In a signed 2's complement representation, overflow or underflow occurs whenever the sign of the two arguments is the same but different from the sign of the result. For example, let A = 01101000 and B = 01011000 be two 8-bit signed 2's complement numbers (A = +104) and (A = +8). Since the sum of these two numbers (192)

overflow underflow is greater than +127, the largest number possible in an 8-bit signed 2's complement representation, an overflow will occur when we add the two numbers. In particular, A + B = 11000000, which indicates a negative result. Problem 2.15 gives another indication of the occurrence of overflow or underflow.

## □ 2.5

### CODING

which each key represents some piece of information such as an alphabetic or numeric character or a control character (e.g., a tab, a space, or a line feed). The key inputs must be converted to some binary form before the computer can process them. This is usually done by assigning a specific pattern of bits to a byte so that there is a byte stored somewhere in the computer's memory to correspond to each keyboard input. One such code is the ASCII code, which will be discussed in Section 2.5.4. Information may also enter the computer from external sensors (such as

thermometers or strain gauges), from switches, from shaft position indicators, and from many other devices. All of this information must be converted in some way to binary for proper handling by the computer. Furthermore, it may be convenient, in some applications, to handle the numbers internally as

It is usually the case that we interact with a computer via a keyboard in

decimal digits which have been suitably encoded in some binary form. This type of representation is very common in hand-held calculators and other devices where numeric information must be constantly entered by a human, processed, and finally returned to the human in numerical form. Many other reasons exist for coding information; among them are encryption and error detection and correction. The purpose of this section,

then, is to describe a few of the commonly used codes and discuss how they are internally handled and how we can convert from one code to another.

#### **Binary-Coded Decimal (BCD)** 2.5.1 and Excess-3 Codes

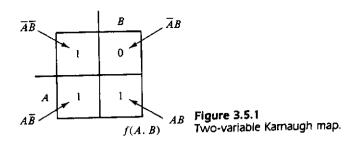

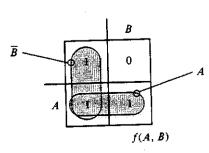

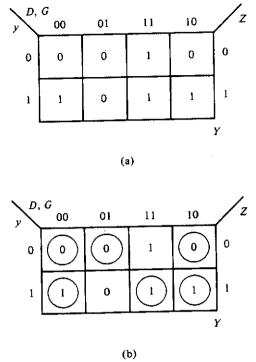

One of the most common internal representations for decimal numbers is the binary-coded decimal, or BCD, representation. In this form, the ten decimal digits are represented by a 4-bit binary number whose value is the decimal digit. For example, the digit 9 is coded as 1001. Figure 2.5.1 gives the code for each of the ten digits. In this form a number such as 1853 would be

| Decimal | BCD  | Excess 3 |                        |

|---------|------|----------|------------------------|

| 0       | 0000 | 0011     |                        |

| 1       | 1000 | 0100     |                        |

| 2       | 0010 | 0101     |                        |

| 3       | 0011 | 0110     |                        |

| 4       | 0100 | 0111     |                        |

| 5       | 0101 | 1000     |                        |

| 6       | 0110 | 1001     |                        |

| 7       | 0111 | 1010     |                        |

| 8       | 1000 | 1011     | Figure 2.5.1           |

| 9       | 1001 | 1100     | BCD and excess-3 code: |

represented internally as 0001 1000 0101 0011. Addition can be carried out in BCD by adding two numbers as if they were binary but with some slight modification to the computational process. Consider, for example, the addition problem 253 + 314. In BCD this becomes

which is, of course, the correct answer. The addition in this example was carried out by simply adding the two numbers in binary. Note that no carries between digits were generated, because the sum in each digit column never exceeded 9. If the sum of two digits is a number greater than 9, then one of two things can happen: either the resulting 4 bits is not a legal BCD code (i.e., it is not one of the ten in Figure 2.5.1), or a carry occurs out of the 4-bit group. An example of the first situation would be the addition of, say, 6 + 8, which in BCD becomes

which is not a legal BCD number. Adding 6 to this result will yield the correct answer (why?). Thus the answer is

$$+ \frac{1110}{0110} + \frac{0110}{10100} = 14 \quad \text{in BCD}$$

The second case will occur for additions such as 8 + 9:

In this case we note that although the low-order 4 bits represents a legitimate BCD number, the result of the addition yields a number greater than 9, as indicated by the carry, and so the correct answer may be obtained once again by adding 6. Thus

$$\begin{array}{r}

1 & 0001 \\

+ & 0110 \\

\hline

1 & 0111 = 17 & \text{in BCD}

\end{array}$$

Consider, as a somewhat more complex example, the problem of finding the sum of 769 and 358, which in BCD becomes

It may happen in carrying out the BCD addition that the result after adding in the 6s and the carries is still not a correct BCD number. If this occurs, we simply apply the correction procedure once more. For example, consider the sum of 37 and 64, which is found as follows:

excess-3

A modified version of BCD, which has some attractive features when subtraction is required, is the excess-3 code. This is basically the same coding as BCD except that each digit has 3 added to it. Figure 2.5.1 gives the specific code values. The attractive characteristics of the excess-3 code is that it is self-complementing; that is, the 1's complement of the coded number yields the 9's complement of the number itself. For example, 3 has a code of 0110, whose 1's complement is 1001, which is the excess-3 code for 6, the 9's complement of 3. Thus subtraction in this binary-coded decimal form can be easily carried out using the diminished radix complement scheme described earlier.

To see how the self-complementing feature of the excess-3 code can be used for subtraction, consider first the addition of two excess-3 numbers, A and B. Adding these two excess-3—encoded numbers is perhaps most easily carried out by first converting each to its BCD equivalent, then adding the results, as described above, and, finally, converting the result back to excess-3. To convert an excess-3—encoded number to BCD is a very simple process. Let X' = X + 3 be an excess-3 digit, where the X is the decimal equivalent of X'. To obtain X we need only add 13 to X' and take the result modulo (16). For example, let X' = 0111, the excess-3 code for 4. Then X' + 1101 = 0111 + 1101 = 1 0100, where we obtain the result modulo (16), 0100, by ignoring the carry. Converting all of the digits of each of the numbers A and B in this way, we obtain the respective BCD representations. For example, to convert the excess-3—encoded representation of the number 97, 1100 1010, to its equivalent BCD representation, we simply add 1101 (13 decimal) to each digit, as follows:

Ignoring the carries generated at each digit position, we obtain the result, 1001 0111, which is, of course, the BCD representation for the decimal number 97.

Now, to perform the subtraction of two excess-3 numbers, say A' - B', we first take the 9's complement of B' by interchanging 0s and 1s in the coded digits. This produces the number  $B'^+$ . Next we convert the numbers A' and  $B'^+$  to their BCD equivalents, A and  $B^+$ . Once this is done, we can add the results in accordance with diminished radix complement arithmetic to produce the difference. The final excess-3-encoded result is found by adding 3

$<sup>^{4}</sup>$  y = x modulo (n) means that y is the remainder obtained upon dividing x by n.

to each digit of the difference. Problems 2.23 and 2.24, at the end of the chapter, explore this process a bit more.

# 2.5.2 BCD-to-Binary and Binary-to-BCD Conversions

When numbers are entered into a computer from, say, a keyboard, they are encoded in some way. A string of encoded digits then needs to be converted to a binary number so that the computer can process the numeric information thus presented. Suppose that the encoding is in BCD.<sup>5</sup> The problem then becomes one of converting these digits to binary. Recall from Section 2.2.2 that converting from decimal to binary requires repeatedly dividing the decimal number by 2 and using the remainder digits as the successive bits of the equivalent binary number. The same can be done for BCD in a very simple way if we make a few observations first.

In the decimal system (or any radix r, system, for that matter) division

by 10, requires only that the radix point be moved one digit position to the left. The remainder is the digit that moves to the right of the radix point. Another way of thinking about this is to assume that the radix point stays fixed and that the number shifts to the right one digit position. Thus, in binary, the number 1001, which is the BCD code for 9, when divided by 2 by shifting right, becomes (maintaining 4 bits in the answer) 0100, with 1 being shifted out of the low-order position. This results in the correct answer of 4 with a remainder of 1. This idea can be used to divide a string of BCD digits by 2 in a very simple manner. Take, for example, 3609/2. In BCD this becomes (0011 0110 0000 1001)/2. Shifting each digit to the right one position will divide that digit by 2, but for the division to be correct for the entire number, a correction must be made as follows. If a 1 is shifted out of some digit position, then 5, that is, (0101) must be added to the next lower digit position (why?). Thus for this example the division may be carried out as

9)/2( 3 6 0 1001)/2= (0011)0110 0000 0000 0100 remainder of 1  $= 0001 \rightarrow 10011$ add 5 as necessary + 0101 1000 0000 0001 0100 8 0 remainder of 1 1 4

shifting

follows:

<sup>&</sup>lt;sup>5</sup> It will be shown in Section 2.5.4 that whatever code is used, it can be converted to BCD. Thus this statement is made without loss of generality.

Using this simple method of division by 2, we can carry out the conversion from BCD to binary. Consider the conversion of 0101 0011 to binary. The work can be organized as follows:

|       | BC      | D value / Binary result (remainder) |

|-------|---------|-------------------------------------|

|       | 0101    | 0011 /                              |

| shift | 0010 →  | 0001 / 1                            |

| add 5 | +       | <u>101</u>                          |

|       | 0010    | 0110 / 1                            |

| shift | 0001    | 0011 / 01                           |

| shift | 0000 →1 | 0001 / 101                          |

| add 5 | +       | <u>101</u>                          |

|       | 0000    | 0110 / 101                          |

| shift | 0000    | 0011 / 0101                         |

| shift | 0000    | 0001 / 10101                        |

| shift | 0000    | 0000 / 110101 = 53 decimal          |

As in Section 2.2.2, this process stops as soon as the dividend goes to zero.

The process of going from binary to BCD is exactly the reverse of the conversion above except that 0101 is subtracted from any BCD digit greater than or equal to 5 before the shift is made and a 1 is set up as a carry into the next-higher-order digit position (why?). An example will illustrate the process. Consider the conversion of 1101101 to BCD. The work may be organized as follows:

|             |      | В             | CD result / Binary | value    |

|-------------|------|---------------|--------------------|----------|

|             |      | 0000          | 0000 / 110110      | 01       |

| shift left  |      | 0000          | 0001 / 10110       | 1        |

| shift left  |      | 0000          | 0011 / 01101       |          |

| subtract 5  |      |               | - <u>0101</u>      |          |

| -           |      | 0000          | 1 0001 / 1101      |          |

| shift left  |      | 0001          | 0011 / 101         |          |

| shift left  |      | 0010          | 0111 / 01          |          |

| subtract 5  |      |               | - <u>0101</u>      |          |

| 340 74 4000 |      | 0010          | 1 0010 / 01        |          |

| shift left  |      | 0101          | 0100 / 1           |          |

| subtract 5  |      | - <u>0101</u> |                    |          |

|             | 0000 | 1 0000        | 0100 / 1           |          |

| shift left  | 0001 | 0000          | 1001               | and stop |

The answer, 109 in BCD, is easily seen to be the correct decimal equivalent of 1101101 binary.

## 2.5.3 Other Codes for Representing Numbers

weighted code

8421 code

parity

The BCD code is an example of a weighted code in which each bit position has a corresponding weight associated with it. The number represented by the code character is found by adding the weights corresponding to each 1 in the code. The weights for the BCD code are 8421, and in fact, the BCD code

of them always 1 and the remaining three bits always 0. Since there are 10 such combinations, each decimal digit will correspond to one such combination. In this representation, if an error occurs, say one that causes a bit to be set to a 1, then the error is readily detected by the fact that the received code does not have exactly two 1s and three 0s. Another simple error-detection techniques.

is sometimes referred to as an "8421 code." Other weighted codes exist and have been used in various computer systems over the years. A weighted code, in order to represent the decimal digits, must have weights which can sum to each of the 9 digits. These weights need not, however, be positive. Figure 2.5.2 gives some examples of other weighted codes. As mentioned earlier, one reason for coding a number might be to permit error detection. One simple error-detection code is the 2-out-of-5 code, in which each digit is represented by a character having 5 bits with two

mechanism is the addition of one extra bit whose value is determined so that the number of 1s in the representation is even (or odd, if one prefers). Such a bit is called a parity bit. If an error occurs in the handling of a number with the result that a single bit is changed, then the total number of 1s will now be odd and it will be evident that an error has occurred. Other codes exist that are capable not only of detecting errors but correcting them as well. Problems 2.26 through 2.28 at the end of the chapter explore some of these coding

| Decimal | 2421 | 84-2-1 | 32211 |

|---------|------|--------|-------|

| 0       | 0000 | 0000   | 00000 |

| 1       | 0001 | 0111   | 00001 |

| 2       | 0010 | 0110   | 00100 |

| 3       | 0011 | 0101   | 00101 |

| 4       | 0100 | 0100   | 00111 |

| 5       | 0101 | 1011   | 01101 |

| 6       | 0110 | 1010   | 10101 |

| 7       | 0111 | 1001   | 10111 |

| 8       | 1110 | 1000   | 11101 |

| 9       | 1111 | 1111   | 11111 |

Examples of weighted codes.

Flaure 2.5.2

Figure 2.5.3 Generation of a 4-bit Gray code.

### Gray code

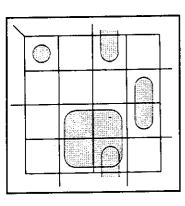

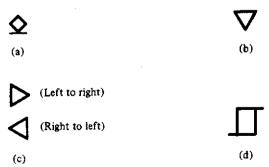

Another very useful and commonly encountered code is the *Gray code*. In this code, successive digits differ in only one bit position. For example, a Gray code sequence for 3 bits would be 000, 001, 011, 010, 110, 111, 101, 100. The generation of this Gray code sequence is very simple. The pattern of changing values of the least significant bit for the first four digits is 01 followed by its reflection 10; then the sequence 01 followed by 10 is repeated as many times as necessary. The next bit from the right has a pattern over *eight* digits of 0011 (twice the number of 0s and 1s) followed by its reflected value 1100. The next bit has the pattern 00001111 (again, twice the number of 0s and 1s) followed by *its* reflected value 11110000. This process continues for as many bits as are in the code. For example, a Gray code for 4 bits is generated as illustrated in Figure 2.5.3. The Gray code is used extensively for shaft encoders and other applications requiring a single bit change between characters.

## 2.5.4 Alphanumeric Codes

Numeric information is not the only information that computers process. Alphabetic characters, punctuation marks, special characters such as mathematical symbols, and many other nonnumeric items must be encoded into a binary form before the computer can properly handle them. One such code is

Char-

acter

@

Α В

C

D

E F G H Ι J K

L M N

0

P

QRSTUV

w

X Y Z

]

**ASCII**

**EBCDIC**

Char-

acter

ASCII

| 40         |                                                                                                                                                                              |     | 60         |            | blank      | 20         | 40         | NUL | 00         |    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|------------|------------|------------|------------|-----|------------|----|

| 41         | C1                                                                                                                                                                           | а   | 61         | 81         | !          | 21         | 5A         | SOH | 01         |    |

| 42         | C2                                                                                                                                                                           | ь   | 62         | 82         | "          | 22         | 7 <b>F</b> | STX | 02         |    |

| 43         | C3                                                                                                                                                                           | С   | 63         | 83         | #          | 23         | 7B         | ETX | 03         |    |

| 44         | C4                                                                                                                                                                           | d   | 64         | 84         | <b>S</b>   | 24         | 5 <b>B</b> | EOT | 04         | 37 |

| 45         | C5                                                                                                                                                                           | е   | 65         | 85         | %          | 25         | 6C         | ENQ | 05         |    |

| 46         | C6                                                                                                                                                                           | f   | 66         | 86         | &          | 26         | 50         | ACK | 06         |    |

| 47         | C7                                                                                                                                                                           | g   | 67         | 87         | '          | 27         | 7D         | BEL | 07         |    |